# CACHE DESIGN SIMULATION IN MULTIPROCESSOR BASED ENVIRONMENT

By Captain Tahir Javaid NC Behram Khan Captain Tasadduq Mahmood Captain Ahmar Raza

Supervisor: Brigadier S.M. Salahuddin Tariq

Project report for partial fulfilment of the requirement of MCS/NUST for the award of the B.E degree in Software Engineering

> Department of Computer Science Military College of Signals Rawalpindi

> > April 2003

# **DECLARATION**

"No portion of the work presented in this dissertation has been submitted in support of another award or qualification either at this institution or elsewhere"

### Acknowledgements

We are thankful to Almighty Allah who enabled us to complete this project. We show gratitude to our parents, whose love and care has enabled us to be what we are. Our deepest appreciation is extended to all whose unfeigned help and encouragement made the present work a reality.

We gratefully acknowledge the help and guidance provided by our project advisors Brigadier S.M.Salahuddin Tariq and Mr. M. Mohsin Rahmatullah. Without their personal supervision, advice and valuable guidance, completion of this project would have been doubtful. We are deeply indebted to them for their encouragement and continual help during this work.

Our very special thanks are extended to Prof. Dr. Mark D Hill and Ms. Carrie Pritchard at University of Wisconsin-Madison, and Ms. Weikel at Virginia State University for their very useful help extended during the project which made us more clear about whole project.

We would like to express our gratitude to all faculty members of the Department of Computer Science for their cooperation and healthy academic environment throughout our career at Military College of Signals Rawalpindi.

### Abstract

The gap between processor and memory speeds is increasing day by day. This situation makes it imperative to use effective caches or other structures between CPUs and DRAMs. The traditional measures of the quality of a caching strategy have been the aggregate hit rate and the execution time of a benchmark, but these measures are no longer sufficient. They provide no insight into dynamic programme behaviour and little guidance in designing a multi-level memory hierarchy. Current caches are designed primarily using ad hoc experimentation and commonly accepted rules-of-thumb: there is no systematic experimental methodology, and there is only fragmented theory to guide the design.

This demands evolution of new methods for evaluating memory system designs before they are implemented in hardware. One such method, trace-driven memory simulation, has been the subject of intense interest among researchers and has, as a result, enjoyed rapid development and substantial improvements during the past decade.

This project report surveys and analyzes these developments by establishing criteria for evaluating Cache Designs for Multiprocessor based Environments using trace-driven simulation method, and then applies these criteria to describe, categorize and recommend optimal combinations of Cache Designs basing on user discretion.

Besides, it provides an analysis methodology that supports cache hierarchy design theoretically and subsequently leads towards the development of mathematical and software tools that accompany this methodology.

In doing so it discusses the strengths and weaknesses of different approaches and uses One Pass Stack based Trace Driven Simulation method for application of Cache Coherence Protocols, to recommend best, appropriate and user defined design, when all criteria, including accuracy, speed, memory, flexibility, portability, ease-of-use and expense are considered.

# Contents

| Chap   | ter 1 Introduction                             | 9                  |  |

|--------|------------------------------------------------|--------------------|--|

| 1.1 Ca | ache and System Performance in Retrospect.     | 9                  |  |

| 1.2 Tr | ace Driven Simulation Methods for Cache Perl   | Formance 10        |  |

| 1.3 Ba | ackground and Related Work in Trace Driven S   | Simulations. 10    |  |

|        | 1.3.1 Trace Collection                         | 10                 |  |

|        | 1.3.2 Trace Reductions                         | 18                 |  |

| 1.4 Tr | race Characteristics                           | 24                 |  |

| Chap   | ter 2 Trace Processing                         | 25                 |  |

| 2.1 Tr | ace Processing: An Overview                    | 25                 |  |

|        | ficient Cache Simulation Using Multiconfigura  | tion Algorithms 26 |  |

| 2.3 St | ack Algorithms                                 | 26                 |  |

|        | 2.3.1 Set Associative Caches                   | 27                 |  |

|        | 2.3.2 Stack Algorithms: Formal Definition      | 28                 |  |

|        | 2.3.3 Linked-List Stack Simulation             | 30                 |  |

|        | 2.3.4 Other Stack Simulation Implementation    |                    |  |

|        | clusion in Set Associative Caches              | 33                 |  |

|        | imulating Direct Mapped Caches with Inclusio   |                    |  |

|        | imulating Set-Associative Caches without Inclu |                    |  |

| 2.7 C  | omparing Actual Simulation Times               | 36                 |  |

| Chap   | ter 3 Implementation                           | 38                 |  |

| 3.1 Pr | emise.                                         | 38                 |  |

| 3.2 Tr | ace-Driven Simulation                          | 38                 |  |

| 3.3 No | on stack Algorithms                            | 41                 |  |

|        | tensions to Stack Analysis                     | 42                 |  |

| 3.5 W  | rite-Back Stack Algorithm                      | 43                 |  |

|        | 3.5.1 The Write-Back Problem                   | 43                 |  |

|        | 3.5.2 A Non Stack Algorithm                    | 43                 |  |

|        | 3.5.3 Dirty Set Inclusion Property             | 44                 |  |

|        | 3.5.4 Writes Avoided.                          | 46                 |  |

|        | 3.5.5 Dirty Push Computation                   | 47                 |  |

|        | 3.5.6 Warm Start.                              | 48                 |  |

|        | rite-Through                                   | 50                 |  |

|        | eletions                                       | 51                 |  |

|        | priodic Write-Back                             | 53                 |  |

| 3.9 Tr | ace-Driven Simulation For Write-Back Caches    |                    |  |

|        | 3.9.1 One-pass Trace-Driven Simulation Al      | ÷                  |  |

|        | Caches.                                        | 53                 |  |

| 2 10   | 3.9.2 An Application Example                   | 60<br>62           |  |

| 3.10   | Other Stack Simulation Implementation          | 62                 |  |

|        | 3.10.1 Inclusion in Set Associative Caches     | 63                 |  |

|        | 3.10.2 Simulating Direct Mapped Caches with Inclusion               | 66  |

|--------|---------------------------------------------------------------------|-----|

|        | 3.10.3 Simulating Set-Associative Caches without Inclusion          | 71  |

| 3.11   | Comparing Actual Simulation Times                                   | 84  |

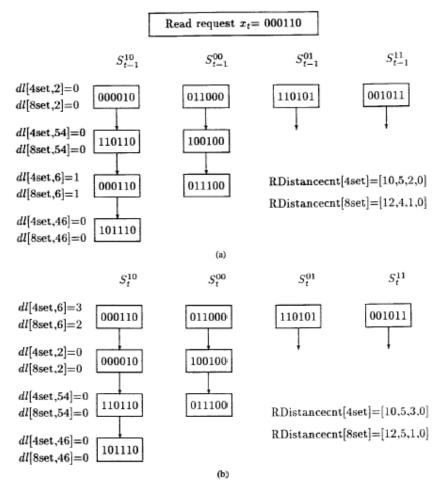

| 3.12   | One-Pass Simulation Technique for Multiprocessor Set-Associative    | -   |

| 0.12   | Caches                                                              | 85  |

| 3.13   | Cache Coherence Protocol for Multiprocessor Set-Associative Caches. | 85  |

| 0110   | 3.13.1 The MESI Protocol                                            | 87  |

| 3.14   | Deletion Issues in Multiprocessor Set-Associative Caches            | 89  |

| 3.15   | Implementation of One-Pass Simulation Technique for Multiprocessor  |     |

|        | Set-Associative Caches                                              | 94  |

| Cl     |                                                                     | 114 |

| Chap   | ter 4 The Acumen                                                    | 114 |

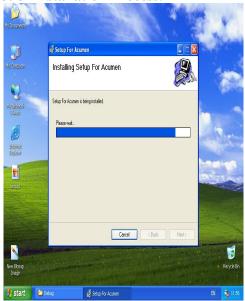

| 4.1 In | troduction to Acumen                                                | 114 |

| 4.2 H  | ow to Use the Software                                              | 114 |

|        | 4.2.1 Screen Shot of Installation Setup                             | 114 |

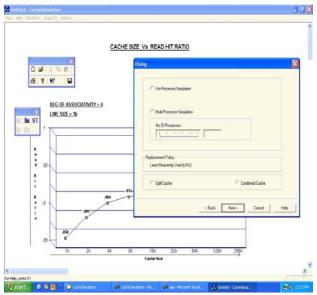

| 4.3 G  | raphical User Interface                                             | 115 |

|        | 4.3.1 Initial Screen                                                | 115 |

|        | 4.3.2 User Input Choices                                            | 115 |

|        | 4.3.3 User Choices of Out Put                                       | 116 |

| 4.4 T  | he Out Put                                                          | 116 |

|        | 4.4.1 Line Graph                                                    | 116 |

|        | 4.4.2 Bar Graph                                                     | 117 |

|        |                                                                     | 110 |

| Chap   | ter 5 Conclusion and Future Prospects                               | 118 |

| 5.1 C  | onclusion                                                           | 118 |

| 5.2 Fu | ature Prospects                                                     | 119 |

| Appe   | ndix A ABC's of Cache                                               | 120 |

| Refer  | rences                                                              | 134 |

# **List of Figures**

# Chapter 2

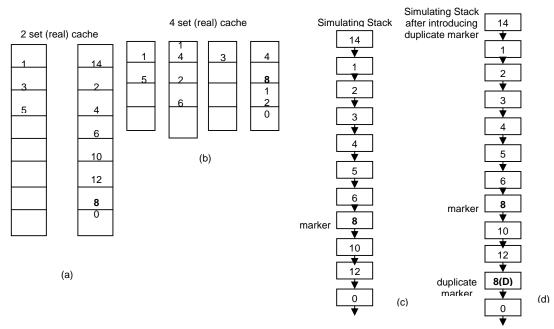

| Figure 2.1 | Set Associative Mapping  | 28 |

|------------|--------------------------|----|

| Figure 2.2 | Stack Simulation Example | 30 |

| Figure 2.3 | Stack Simulation Storage | 31 |

| Figure 2.4 | Stack Simulation         | 31 |

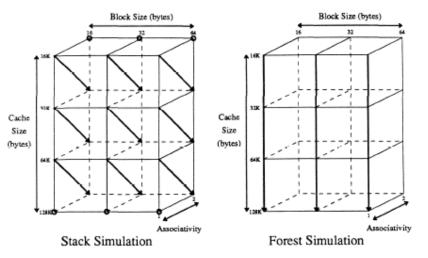

| Figure 2.5 | Forest Simulation        | 34 |

| Figure 2.6 | Stack Simulation Example | 35 |

## Chapter 3

| Figure | 3.1  | Examples of Stack Maintenance Using LRU Replacement               | 39 |

|--------|------|-------------------------------------------------------------------|----|

| Figure | 3.2  | Examples of Stack Maintenance Using a Stack Replacement Algorithm | 39 |

| Figure | 3.3  | General Stack Algorithm                                           | 40 |

| Figure | 3.4  | The Stack Analysis Algorithm                                      | 41 |

| Figure | 3.5  | Cache Contents Using the Least Frequently Used Policy             | 41 |

| Figure | 3.6  | Cache Contents Using One-Block Demand Prefetch Policy             | 42 |

| Figure | 3.7  | General Non Stack Write Back Algorithm                            | 44 |

| Figure | 3.8  | Write Back Stack Algorithm                                        | 47 |

| Figure | 3.9  | Revised Count of Dirty Pushes After Warm Start                    | 49 |

| Figure | 3.10 | Mixed Write-Back/Write Through Algorithm                          | 50 |

| Figure | 3.11 | A Gap "jumps" Down the Stack                                      | 51 |

| Figure | 3.12 | Write-Back Stack Algorithm with Delete                            | 52 |

| Figure | 3.13 | An Example of Mattson (1970) Algorithm                            | 54 |

| Figure | 3.14 | A Block can have Different Dirty Levels in Caches                 | 55 |

| Figure | 3.15 | An Outline of an Algorithm for Simulating Write-Back Caches.      | 56 |

| Figure | 3.16 | A Snapshot Example for the One-Pass Write-Back Algorithm          | 58 |

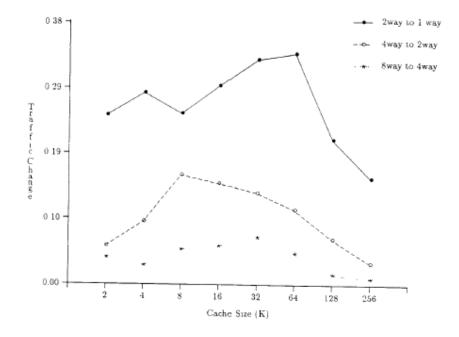

| Figure | 3.17 | Relative Traffic Change Vs. Cache Size (8-byte block size)        | 59 |

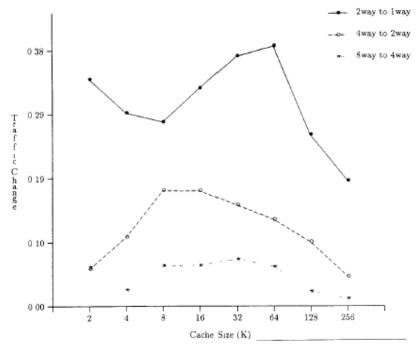

| Figure | 3.18 | Relative Traffic Change Vs. Cache Size (16-byte block size)       | 60 |

| Figure | 3.19 | Relative Traffic Change Vs. Cache Size (32-byte block size)       | 61 |

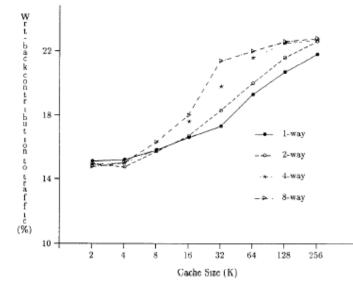

| Figure | 3.20 | Percentage Contribution of Write-Back to Total Traffic.           | 62 |

| Figure | 3.21 | Forest Simulation                                                 | 67 |

| Figure | 3.22 | Forest Simulation Example                                         | 68 |

| Figure | 3.23 | Forest Simulation Storage                                         | 68 |

| Figure | 3.24 | Forest Simulation Storage                                         | 68 |

| Figure | 3.25 | Cache Design Space                                                | 71 |

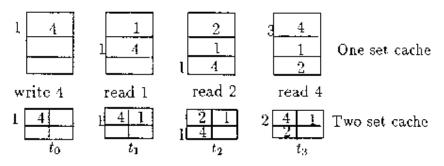

| Figure | 3.26 | Stacks for Caches with One or Two Sets Using Bit Selection        | 72 |

| Figure | 3.27 | Concurrent Stack Simulation with Shared Storage                   | 74 |

| Figure | 3.28 | All-Associativity Simulation Example                              | 75 |

| Figure | 3.29 | All-Associativity Simulation Storage                              | 76 |

| Figure | 3.30 | All Associativity Simulation                                      | 77 |

| Figure | 3.31 | All-Associativity Simulation with Set Hierarchy Example           | 78 |

| Figure |      | All Associativity Storage w/ Set Hierarchy                        | 79 |

| Figure | 3.33 | All Associativity Simulation w/ Set Hierarchy                     | 80 |

| Figure | 3.34 | Random Replacement Does Not Work                                  | 82 |

| Figure | 3.35 | Deletion Issue (In case of Miss : Initial States)                | 90 |

|--------|------|------------------------------------------------------------------|----|

| Figure | 3.36 | Deletion Issue (In case of Miss : States after Hole Propagation) | 91 |

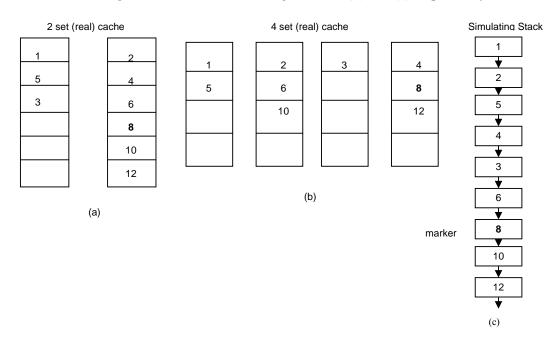

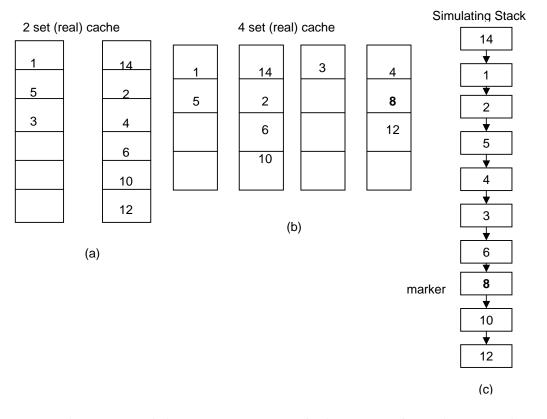

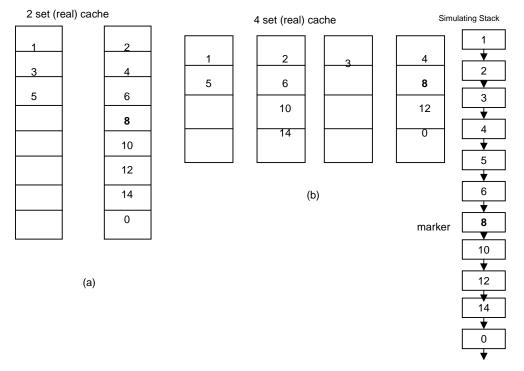

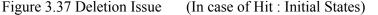

| Figure | 3.37 | Deletion Issue (In case of Hit : Initial States)                 | 92 |

| Figure | 3.38 | Deletion Issue (In case of Hit : States after Hole Propagation)  | 93 |

# Chapter 4

| Figure 4.1 | Installation Process | 114 |

|------------|----------------------|-----|

| Figure 4.2 | Input Screen         | 115 |

| Figure 4.3 | User Input           | 116 |

| Figure 4.4 | Out Put Choices      | 116 |

| Figure 4.5 | Line Graph           | 117 |

| Figure 4.6 | Bar Graph            | 117 |

### **Chapter One**

### Introduction

1.1 Cache and System Performance in Retrospect.

Cache: a safe place for hiding or storing things.

Webster's New World Dictionary of the American Language, Second College Edition (1976)

Cache is the name generally given to the first level of the memory hierarchy encountered once the address leaves the CPU. Since the principle of locality applies at many levels, and taking advantage of locality to improve performance is so popular, the term cache is now applied whenever buffering is employed to reuse commonly occurring items: examples include file caches, name caches, and so on. The memory hierarchy is given the responsibility of address checking: hence protection schemes for scrutinizing addresses are also part of the memory hierarchy.

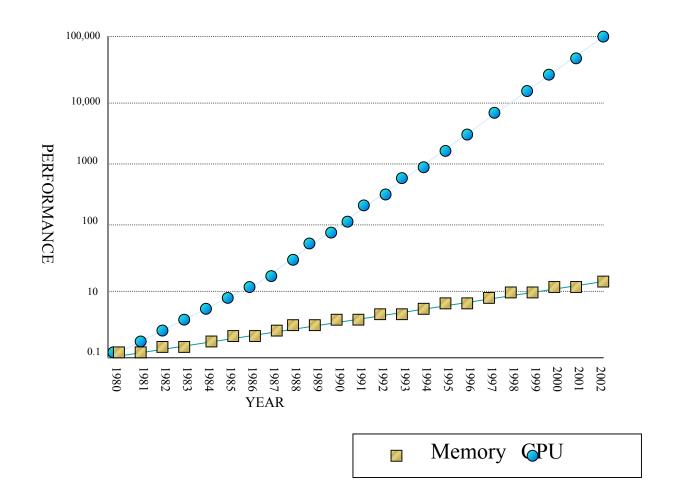

The importance of the memory hierarchy has increased with advances in performance of processors. For example, in 1980 microprocessors were often designed without caches, while in 1995 they often came with two levels of caches. Microprocessor performance improved 55% per year since 1987, and 35% per year until 1986.

Computer pioneers correctly predicted that programmers would want unlimited amounts of fast memory. An economical solution to that desire is a memory hierarchy, which takes advantage of locality and cost/performance of memory technologies. The principle of locality says that most programs do not access all code or data uniformly. This principle, plus the guideline that smaller hardware is faster, led to the hierarchy based on memories of different speeds and sizes. Since fast memory is expensive, a memory hierarchy is organized into several levels each smaller, faster and more expensive per byte than the next level. The goal is to provide a memory system with cost almost as low as the cheapest level of memory and speed almost as fast as the fastest level. The levels of the hierarchy usually subset one another: all data in one level is also found in the level below, and all data in that lower level is found in the one below it, and so on until we reach the bottom of the hierarchy. Note that each level maps addresses from a larger memory to a smaller but faster memory higher in the hierarchy. As part of address mapping, where miss rate is the fraction of accesses that are not in the cache and miss penalty is the additional clock cycles to service the miss, a block is the minimum unit of information that can be present in the cache (hit in the cache) or not (miss in the cache).

#### 1.2 Trace Driven Simulation Methods for Cache Performance.

Caches have been widely used in most computer systems for the last two decades. They are expected to play an increasingly important role in future high-performance computer systems. Very soon we will see machines with an off-chip cache miss penalty of over 100 instruction times (undoubtedly, the performance of these machines will be substantially influenced by their cache performance). A careful cache design choice is therefore crucial to the design of future computer systems. The most accurate way of assessing cache performance before a machine is built would be a thorough simulation of the whole system, which captures not only the detailed behaviour of the cache but also its subtle interactions with the rest of the system. Unfortunately, a thorough simulation of a complete system generally takes too long to allow coverage of the vast design space.

A more realistic approach would loosely couple the cache with the rest of the system via high-level analytical model. In this approach, detailed simulations are performed on the cache subsystem to produce performance metrics such as miss ratios and write-back traffic. These results are then incorporated into the high-level model to generate the system performance under different cache design choices.

Still, even cache simulation itself is not an easy task. The widely used tracedriven cache simulation technique generally requires a large amount of disk space to store the program traces, and simulations that produce results which would cover a sufficient portion of the design space are very time consuming. Therefore, methods which can quickly and cheaply produce cache performance results are desirable.

A large number of techniques for trace-driven cache simulation have been reported in the literature. Related work is briefly reviewed in following section along with a description of trace characteristics that we use throughout this paper.

#### 1.3 Background and Related Work in Trace Driven Simulations.

Trace driven simulations can be further subdivided under three major headings, which are:

- Trace Collection

- Trace Reduction

- Trace Processing

Out of these three each one is a complete subject within itself. Though the main focus of our project is on *Trace Processing* however following sections of this chapter briefly discuss 'trace collection' and 'trace reduction' for the sake of completeness, whereas a detailed discussion on trace processing is generated in chapter 2.

#### 1.3.1 Trace Collection

To ensure accurate simulations, collected address traces should be as close as possible to the actual stream of memory references made

by a workload when running on a real system. Trace quality can be evaluated based on the completeness and detail in a trace, or on the degree of *distortion* that it contains. Ideally speaking a *complete* trace should include all memory references made by each component of the system, including all user-level processes and the operating system kernel. User level processes should include not only applications, but also OS server and daemon processes that provide services such as a file system or network access. Complete traces should also include dynamically-compiled or dynamically-linked code, which is becoming increasingly important in applications such as processor or operatingsystem emulation. An ideal *detailed* trace is one that is annotated with information beyond simple raw addresses. Useful annotations include changes in VM page-table state for translating between physical and virtual addresses and tags that mark each address with a reference type (read, write, execute), size (word, half word, byte) and a timestamp. Traces should be *undistorted* so that they do not include any additional memory references, or references that appear out of order relative to the actual reference stream of the workload had it not been monitored. Common forms of distortion include *trace discontinuities*, which occurs when tracing must stop because a trace buffer is not large enough to continue recording workload memory references, and time dilation and memory dilation, which occur when the tracing method causes a monitored workload to run slower, or to consume more memory than it normally would.

In addition to the three aspects of trace quality described above, a good trace collector exhibits other characteristics as well. In particular, *portability*, both in moving to other machines of the same type and to machines that are architecturally different is important. Finally, an ideal trace collector should be *fast*, *inexpensive* and *easy to operate*.

Address traces have been extracted at virtually every system level, from the circuit and microcode levels to the compiler and operating-system levels. (see Figure 2). We organize the following discussion accordingly, starting at the lower hardware levels.

#### 1.3.1.1 External Hardware Probes

A straightforward method for collecting address traces is to record signals from electrical probes physically connected to the address bus of a host computer while it runs a workload. The address and control signals are fed into an external memory buffer at the full speed of the monitored host system, and when the buffer fills, its contents are transferred to a standard storage device, such as tape or disk, so that it can be processed at a later time. If a long, continuous address trace is desired, then the buffer must either be very large or there must be some way to stall the host whenever the buffer becomes full. It is usually only possible to stall the processor — external I/O devices, such as disks or network controllers will must usually be permitted to continue operating. If there is no way to stall the system, then several discontinuous address-trace samples can be acquired and concatenated together. In either case, the resulting trace exhibits a form of distortion that is called *trace discontinuity*.

The main advantage of the probe-based trace collectors is their ability to capture trace sequences complete with both user and kernel memory references, and free of most forms of trace distortion, provided that the trace buffer is deep enough. Although the traces are complete, this does not necessarily mean that they are easy to interpret. Hardware events such as cache misses, integer- and floating-point-unit stalls, exceptions and interrupts all must be separated from run cycles to determine the actual type (read, write, execute) and size (word, half word, byte) of the memory references made by a monitored processor. In processors that implement hardware pre-fetching or speculative execution, it may be difficult or impossible to separate "true" memory references from those that occur due to a pre-fetch that might not actually be used. Some of these problems can be overcome by implementing the inverse function of the processor sequencer, either in the trace-collecting hardware, or in a trace post-processing tool. Because the addresses captured by a probebased monitor are usually physical addresses, special methods that may require cooperation from the host OS must be used to reverse-translate addresses to their matching virtual addresses. These problems all follow from the fact that probe-based trace collectors are external to the monitored system and therefore do not have easy access to operating-system data structures.

A common misconception regarding trace collection using hardware probes is that the technique is very fast. While it is true that acquisition of the trace proceeds at the full speed of the monitored system, it is important to account for the overhead of managing trace-buffer overflow as well as the time required to empty the buffer. This overhead is typically not reported in published papers, but because most systems can unload these buffers only through some form of relatively low-bandwidth channel, this overhead is necessarily high. For a system where overhead data is available, approximately 12 hours are required to obtain 11 seconds of real-time system activity.

Although trace collection with hardware probes is time consuming, once the traces have been captured and stored to a permanent file they require no special hardware to use, and can be used repeatedly to achieve reproducible simulation results. Hardware probe-based methods share other common disadvantages. The first is expense. Logic analyzers with deep trace memories cost from \$50,000 to \$200,000. These amounts are probably low compared to the engineering costs associated with designing custom hardware. A second problem is portability. Although logic analyzers support probes for most popular microprocessors, it is often necessary to physically modify the motherboard or chassis of the monitored system to enable probe access to the signals of interest. These systems also require an understanding of the electrical issues concerning the connection of probes to running hardware, and are therefore typically fragile, sensitive to their operating environment, and difficult to learn and operate.

As noted above, the advent of on-chip caches is making it increasingly difficult to build trace collection hardware as an afterthought. The future of probe-based trace collection therefore depends mainly on the level of support *designed* into systems for this task. A small, on-chip trace buffer that traps to the operating-system kernel whenever it becomes full is an example of the sort of support that could be provided. However, even a very small buffer of 2048 entries with 32-bits per entry (8 K-bytes) is about the size of on-chip caches in current microprocessors and thus would be relatively costly in terms of chip area. An alternative approach would be to send certain key internal signals through the microprocessor package pins so that they can be monitored externally.

#### 1.3.1.2 Microcode Modification

The high cost of circuit-level probing has motivated many researchers to develop methods for collecting traces at higher levels of system abstraction. One such alternative is to collect traces at the borderline between the hardware and software levels of a system in microcode. From the beginnings of the IBM 360 series (1964) until the DEC VAX machines, the most common method for implementing control logic was microcode. When implemented off-chip, a microcode memory was often writable or could be modified through replacement, making it possible to change the behaviour of instructions, or to support multiple instruction sets. Agarwal (1986, 1988) realized that this mechanism made it possible to collect address traces. He modified the microcode on a VAX 8200 to cause all instructions to deposit the addresses of their memory references into a reserved area of main memory as a side effect of their execution. This method, which Agarwal called address tracing using microcode (ATUM), offers a number of advantages. The first is completeness. Because the microcode runs beneath the operating system, all user and kernel references are captured, as well as those from dynamically-compiled and dynamicallylinked code. Because ATUM has access to internal system state, it is easily able to annotate traces with access-type tags and page-map information. Another advantage is speed. ATUM acquires address traces with a slowdown of only about 10 to 20, and because the addresses can be processed directly out of the trace buffer in main memory, there is no overhead of buffer unloading as with external probe-based trace collection. Finally, no additional hardware is required. The only cost associated with ATUM is the engineering effort required to modify microcode to produce the desired results. The ATUM method suffers a few minor disadvantages and one major one. First, ATUM traces exhibit some discontinuity distortion because the processor is not stalled when the trace buffer becomes full. Buffer size could be increased only up to a certain point because it took away from the usable memory of the host system. Agarwal has developed a method, called *trace stitching*, to counter this problem. Microcode modification also introduces another form of trace distortion, commonly called *time dilation*. Because instructions take 10 to 20 times as long to execute as they normally would, external devices such as disks and network controllers appear to the workload to be faster than they actual are, and interrupts from the system clock occur more frequently, thus changing the workload's behaviour.

The primary disadvantage of the microcode-modification technique is that the technique is now effectively obsolete because most new microprocessors use hardwired control or have an on chip microcode memory that is not easily modified. The fundamental idea behind microcode modification ---augmenting the interpretation of instructions to generate trace addresses as a side effect of their execution — can, however, be implemented at other levels in a system. This has been made easier by some of the very trends that have made microcode modification obsolete. Hardwired control, for example, has been made possible (or at least easier) with the advent of RISC instruction sets. The relatively simple and uniform coding of RISC instruction sets has also made it easier to develop fast instruction-set emulators and binary-rewriting tools for annotating executables to produce traces as a side effect of their normal execution.

#### 1.3.1.3 Instruction-set Emulation

An instruction-set architecture (ISA) is the collection of instructions that defines the interface between hardware and software for a particular computer system. A microcode engine, as described in the previous section, is an ISA interpreter that is implemented in hardware. It is also possible to interpret an instruction set in software through the use of an *instruction-set emulator*. Emulators typically execute one instruction set (the *target* ISA) in terms of another instruction set (the *host* ISA) and are usually used to enable software development for a machine that has not yet been built, or to ease the transition from an older ISA to a newer one. As with microcode, an instruction-set emulator can be modified to cause an emulated program to generate address traces as a side-effect of its execution.

wisdom holds Conventional that instruction-set emulation is very inefficient, with slowdowns estimated to be in the range of 1,000 to 10,000 Agarwal (1989); Wall (1989); Borg(1989); Stunkel(1991); Flanagan(1992). The degree of slowdown is clearly related to the level of emulation detail. For some applications, such as the verification of a processor's logic design, the simulation detail required is very high and the corresponding slowdowns may agree with those cited above. In the context of this review, however, we consider an instructionset emulator to be sufficiently detailed for the purposes of address-trace collection if it can produce an accessible trace of memory references made by the instructions that it emulates. Given this minimal requirement, there are several recent examples of instruction-set emulators that have achieved slowdowns much lower than 1,000; they work by fetching, decoding and then dispatching instructions one at a time in an iterative emulation loop, re-interpreting instructions each time they are encountered. Instructions are fetched by reading the contents of the emulated program's text segment, and are decoded through a series of mask and shift operations to extract the various fields of the instruction (opcode, register specifiers, etc.). Once an instruction has been decoded, it is emulated (dispatched) by updating machine state, such as the emulated register set, which can be stored in memory as a virtual register data structure, or which may be held in the actual hardware registers of the host machine. An iterative interpreter may use some special features of the host machine to speed instruction dispatch, but this final step is more commonly preformed by simply jumping to a small subroutine or *handler* that updates machine state as dictated by the instruction's semantics. The reported slowdowns for iterative emulators range from 20 to about 600, but these figures should be interpreted carefully because larger slowdowns may represent the time required to emulate processor activity that is not strictly required to generate address traces.

Some interpreters avoid the cost of repeatedly decoding instructions by saving *predecoded* instructions in a special table or cache. A predecoded instruction typically includes a pointer to the handler for the instruction, as well as pointers to the memory locations that represent the registers on which the instruction operates. The register pointers save both decoding time as well as time in the instruction handler, because fewer instructions are required to compute the memory address of a virtual register.

#### 1.3.1.4 Static Code Annotation

The fastest instruction-set emulators dynamically translate instructions in the target ISA to instructions in the host ISA, and optionally annotate the host code to produce address traces. Because these emulators perform translation at run time they gain some additional functionality, such as the ability to trace dynamically-linked or dynamically-compiled code. This additional flexibility comes at some cost, both in overall execution slowdown and in memory usage. For the purposes of trace collection, it is often acceptable to trade some flexibility for increased speed. If the target and host ISAs are the same and if dynamically-changing code is not of interest, then a workload can be annotated *statically*, before run time. With this technique, instructions are inserted around memory operations in a workload to create a new executable file that deposits a stream of memory references into a trace buffer as the workload executes. Static code annotation can be performed at the source (assembly) level, the object-module level, or the executable (binary) level, with different consequences for both the implementation and the end user Stunke(1991); Wall(1992); Pierce(1994).

The main advantage of annotating code at the source level is ease of implementation. At this level, the task of relocating the code and data of the annotated program can be handled by the usual assembly and link phases of a compiler, and more detailed information about program structure can be used to optimize code-annotation points. Unfortunately, annotation at this level may render the tool unusable in many situations because the complete source code for a workload of interest is often not available and annotation at this level is also the most difficult to implement because executable files are often stripped of symbol-table information. A significant amount of analysis may be required to properly relocate code and data after trace-generating instructions have been added to the program Pierce(1994). Despite these difficulties, there exist several program-annotation tools that operate at the executable level. A common problem with many code annotators is that they produce traces with an inflexible level of detail, requiring a user to select the monitoring of either data or instruction references (or both) with an all-or-nothing switch. Many tools are similarly rigid in the mechanism that they use to communicate addresses, typically forcing the trace through a file

or pipe interface to another process containing the trace processor. Some more recent tools overcome these limitations and offer a flexible interface that enables a user to specify how to annotate each individual instruction, basic block and procedure of an executable file; at each possible annotation point the user can specify the machine state to extract, such as register values or addresses, as well as an analysis routine to process the extracted data. If no annotation is desired at a given location, they do not add it, thus enabling a minimal degree of annotation to be specified for a given application. For I-cache simulation, for example, a simulator writer can specify that only instruction references be annotated, and that a specific I-cache analysis routine be called at these points. In general, code annotators are not capable of monitoring multi-process workloads or the operating system kernel, but there exist some exceptions as well.

#### 1.3.1.5 Single-step Execution

The highest level of system abstraction for collecting address traces is the operating system. Most operating systems support some form of debugging utility that enables a programmer to step through a program one instruction at a time to expose errors. This form of debugging is usually supported in hardware through a single-step execution mode, where the processor traps into the OS kernel after the execution of each instruction or basic block Digital 86; AMD91; AMD93; Motorola93; HP90; Motorola90 or by breakpoint instructions that cause kernel traps whenever they are executed Kane(1992); Intel(1990). A debugger that supports single-step execution and examination of processor state, such as registers, can be modified to generate both instruction-address and data-address traces. Instruction-address traces are produced by simply recording the value of the program counter at each execution step. Data-address traces require instruction emulation to determine if the current instruction generates a memory reference and, if so, the value of that reference.

The main advantages of this method are low expense, high portability, and ease of use. With the exception of debugger data structures, little additional host memory is used. Unfortunately, slowdowns for this technique are high, with estimates varying widely from 100 Agarwal (1988) to 1,000 Flanagan (1992) to 10,000 (Holliday1991). High slowdowns are usually due to debugger implementations that rely on the UNIX ptrace () facility which, in turn, is implemented using UNIX exception-signal handlers. Although there is nothing inherent in this approach that limits traces to a single process, or to user-only references, debuggers typically do impose these limitations. Similarly, dynamically compiled and dynamicallylinked code is usually not supported by debuggers. Because only address-trace information is desired, a single-step tracecollection tool could, in principle, be written from scratch to avoid the overheads and single-process limitations of program debuggers. We are not aware of any existing trace-collection system that uses this approach.

#### 1.3.2 Trace Reductions.

Since the space and time needed for trace-driven cache simulation are approximately proportional to the trace length, several early studies have focused on reducing the trace length to reduce the cost of cache simulation. Smith (1977) pioneered this work by proposing a trace deletion technique for memory-paging studies. He used Least Recently Used (LRU)-model of memory references and produced a reduced trace by deleting references that accessed the top D levels of the LRU stack of data. The resulting trace, if used for simulating memory larger than D pages under the LRU replacement algorithm, would produce almost the same number of misses (page faults) as the original long trace, provided that the page size is kept constant.

An extension of Smith's (1977) technique was proposed by Puzak (1985). He called it trace stripping. This approach focuses on reducing traces for simulating set-associative caches. A direct-mapped cache (serving as a filter) is simulated and the miss references are recorded; they form a reduced trace. This reduced trace, if used to simulate caches with a larger number of sets, would result in the same number of misses as the original trace, provided that the block size is kept the same.

Other approaches have also been proposed which substantially reduce the trace length but cannot guarantee that exact performance metrics would be obtained by using the reduced trace. For example, Smith's(1977)'s snapshot method records memory references at regular time intervals; a set selection method described by Puzak(1985) keeps only references that access some specific sets; Agarwal's(1987) trace compaction combines Puzak's(1985) reduction technique and Smith's(1977)'s snapshot method ; Laha et al.(1988), proposed another sampling-based method.

The main focus is to produce exact cache performance cheaply and quickly. To this end, sampling approaches cannot be used. Even Puzak's (1985) and Smith's (1977)'s original exact reduction techniques are not sufficient for two reasons. First, the reduced trace method can only produce a count of misses (i.e., hit ratios) but not the number of write-backs. Second, the existing methods apply only to uniprocessor caches and are inadequate for multiprocessor caches. Finally, the reduced trace cannot be used to simulate caches which have block sizes different from that of the cache filter used for the trace reduction.

#### 1.3.2.1 Trace Reduction for Write-Back Cache Simulation.

As stated earlier, the objective of trace reduction is to produce a reduced trace which can be used to generate exactly the same number of misses and write-backs as the original trace. Wang(1991) used small direct-mapped cache as a filter but instead of keeping only references that cause misses, he also kept those that were first-time writes.

The intuitive idea behind this reduction is that if a reference causes a hit in a small direct-mapped cache, it will also hit in a larger cache. Furthermore, if a block is dirty in a small direct-mapped cache it will also be dirty in a larger cache. Thus, the miss references to a small cache would be a superset of misses to larger caches. Also, references that cause blocks to be dirty in a small cache would be a superset of references that make blocks dirty in larger caches. Therefore, the reduced trace can be used to produce exact cache performance metrics for same size or larger caches (which implies some criteria for the parameters of the small cache).

#### Formal description of reduction is as follows.

Assume all caches under study have a power-of-two integer number of sets, simulate a direct-mapped cache with S sets using a program trace and record only references that cause misses or writes on clean data to form a reduced trace. This reduced trace, if used to simulate caches with a larger number of sets, would produce exactly the same number of misses and write-backs as the original trace, provided that the same block size is used.

#### Now we see the proof of the above statement,

**Proof**. The proof on the exact number of misses was given by Puzak (1985). So, it is sufficient to prove that using the reduced trace would produce the same number of write-backs as the original trace. Since the number of misses is exactly the same, any block that is replaced is the same independently of whether the reduced trace or the original trace is used. For the purpose of proof by contradiction, let us assume that there is a block, when replaced using the reduced trace that has a dirty state different from the original trace. That is, we have two cases:

(1) Case 1: the block is clean using the reduced trace, but is dirty using the original trace. The reasons for a block to be dirty are either the block is brought into the cache upon a write miss or upon a read miss followed by a write-on-clean. In the case of a write miss, there will be a write miss in the filter cache too, and the reduced trace will retain the reference. That is, using the reduced trace will make the block dirty too. In the case of a write-on-clean, it can be either a write-on-clean or a write miss on the filter cache. In either case, the write reference is recorded in the reduced trace. Thus, using the reduced trace will make the block dirty as well.

(2) Case 2: the block is dirty using the reduced trace, but is clean using the original trace. This case is easily dismissed as follows. Since the block is clean using the original trace, the block must have been brought into the cache on a read miss and possibly followed by a number of read references. The first read miss and possibly a subset of the followed read references will be recorded in the reduced trace. None of them will cause the block to be dirty, since they are read references. Thus, using the reduced trace will make the block clean as well. For both cases, the block will be in the same dirty state using either the original trace or the reduced trace. This contradicts the assumption that the block be in different states. Since a block being replaced cannot have different dirty states and since the number of replacements is the same, using the reduced trace will produce the same number of write-backs as the original trace.

Wang (1991) used the traces mentioned above to measure the effectiveness of trace reduction. By using an 8K-byte cache filter with a 4-byte block size obtained reduced traces which are between 10 and 22 times shorter than the original traces.

The reduced traces were used to simulate (i.e., record misses and number of write-backs) a 32 K-byte 4-way setassociative cache. Table I shows that the simulation times are between 7 and 15 times faster using the reduced traces. We notice from Table I that the speedups are not as good as the space reduction ratios. This is due to the fact that the reduced traces have fewer localities than the original traces.

#### 1.3.2.2 Multiblock-Size Trace Reduction.

The reduction techniques we have discussed so far only work if reduced traces are used to simulate caches with the same block size as that of the filter cache used for reduction. A reduced trace cannot be used to simulate a large cache with a different block size because the contents of a larger cache are not necessarily a superset of those of a smaller cache with different block sizes. Thus, the reduced trace may not capture every miss that can occur in a larger cache. In other words, the reduced trace cannot be used to simulate larger caches and still produce the exact results.

What this lack of consideration implies is that we need to produce reduced traces for every possible block size under study or we take the risk of getting incorrect results. Unfortunately, the disk spaced needed to store every reduced trace would take away the space-saving benefits of the trace reduction. A "universal" reduced trace that can be used for all different block sizes but does not take up too much space is therefore highly desirable.

Table I Time and Space Saving Due to Trace Reduction

| traces                     | Pero      | Thor      | Pops      |

|----------------------------|-----------|-----------|-----------|

| original length            | 14,198kB  | 16,415kB  | 16,087kB  |

| reduced trace length       | 624kB     | 1,045kB   | 1,519kB   |

| space reduction            | 22.7      | 15.7      | 10.6      |

| simu. time for orig. trace | 208.7 sec | 246.6 sec | 268.3 sec |

| simu, time for redu, trace | 14.4 sec  | 26.8 sec  | 39.6 sec  |

| speed-up                   | 14.5      | 9.2       | 6.8       |

In an attempt to produce a universal reduced trace, we observe that most misses to a cache filter with one block size tend to be misses in another filter with a different block size. Therefore, Wang(1991) produce universal reduced traces by collecting the superset of misses that occur on every cache filter with different block sizes. His results (Table II) show that with 40-48% of additional space, i.e., 1.8-4.5% of the original traces, we can have universal reduced traces for 5 block sizes. We notice from TableII that there is a jump on the length of the reduced trace from 4 block sizes to 5 block sizes for the Pops trace. The reason this happens is that the Pops trace has the worst locality among the three traces and the 8 K-byte cache filter experiences lots of misses due to thrashing when the block size is 64 bytes.

# 1.3.2.3 Trace Reductions for Parallel Multiprocessor Cache Simulation.

Recently, there have been many performance (trace-driven simulation) studies on cache coherence protocols for shared-bus multiprocessors. In this section we describe how multiprocessor traces can be reduced and still be used to provide exact performance figures. The performance metrics of interest for multiprocessor caches are miss ratios, number of write-backs and cache-coherence interferences from other caches. We start our discussion with a straightforward sequential simulation and describe how traces can be reduced for this type of simulation. We then consider extensions of the reduction technique to parallel cache simulations.

A few assumptions are in order before we present the reduction technique, these assumptions were originally made by Wang(1991) and we apply them here for our discussion. We assume that each processor has a private cache and that the cache size is the same for every cache in the system. We also assume that the relative order of reference streams from each processor is kept the same across different simulations; similar assumptions are presented by Thompson (1989) and Lin et al. (1989). To simplify our discussions we further assume that an invalidation protocol Sweazey (1986) is used for cache coherence, although our results can easily be extended to a larger class of coherence protocols. For the MOESI class of invalidation protocols, each cache block can be in one of four states: invalid, private, shared and dirty. On a read miss, the block is brought in and the state is set to private if the other caches do not have this block: otherwise the state is set to shared. On a write miss the block is brought in and any copy of this block, if present in other caches, is invalidated before the write is done. The state is set to dirty. On a write hit on a shared block, other copies also get invalidated before the write is done and

Table II Length of Reduced Traces with up to 5 Different Block Sizes

| traces                                  | Pero        | Thor          | Pops           |

|-----------------------------------------|-------------|---------------|----------------|

| original length                         | 14,198kB    | 16,415kB      | 16,087kB       |

| redu. length (4 byte block size)        | 624k (4.4%) | 1,045k (6.4%) | 1,519k (9.4%)  |

| redu. length (4b and 8b)                | 731k (4.9%) | 1,186k (7.2%) | 1.643k (10.2%) |

| redu. length (4b, 8b and 16b)           |             |               | 1,719k (10.7%) |

| redu. length (4b, 8b, 16b and 32b)      | 828k (5.8%) | 1,353k (8.2%) | 1.795k (11.2%) |

| redu. length (4b, 8b, 16b, 32b and 64b) | 878k (6.2%) | 1,453k (8.9%) | 2,247k (13.9%) |

the state is set to dirty. A write hit on a private block does not require a bus transaction except that the state of the block is changed to dirty.

A straightforward simulation method represents a cache as a table and takes a serialized reference stream as input. For each reference a table look-up is performed to determine whether there is a hit and whether any coherence action needs to be done. Although this straightforward serial method is slow, we use it as the basis for comparing the speed-up with parallel methods to be discussed later.

The trace reduction for this method works as follows. Simulate small caches (serving as filters) under the chosen coherence protocol using a multiprocessor trace and record only references that cause misses or result in writes on clean blocks. These references form a reduced trace and, if used for simulating large multiprocessor caches, would produce the same number of misses, write-backs, and invalidations as the original trace, provided that the block size is kept the same and the same coherence protocol is used.

The proof of the above statement is similar to that of the uniprocessor case, except we need to prove that the reduced traces preserve the references that cause invalidations i.e. if the original trace is used to simulate a larger cache (more sets) it should produce the same number of invalidations as the reduced trace. To show this, let us assume, for the purpose of a proof by contradiction, that there are invalidations in the original trace but not in the reduced trace. Then, there must be a first such invalidation. According to our chosen protocol (to mention again this protocol was originally designed by Wang (1991) and we are only discussing it here), this invalidation can either be caused by a write miss or a write hit on shared data (i.e., a subset of write on clean) in the large cache. If this is a write miss, then there will also be a write miss in the filter cache, so this reference will be recorded in the reduced trace. If this is a write hit on shared data, then it can only fall into the following three categories in the filter cache: namely, a write hit on shared data, a write hit on private, or a write miss. It cannot be a write hit on a modified block in the filter cache, since before this first mismatched invalidation a block that is modified in the filter cache will also be modified in the larger cache. That is, the reference causes either a write on clean or a write miss in the filter cache, and it will be recorded in the reduced trace as well. This is a contradiction to the assumption that the reduced trace does not contain the reference that causes the invalidation. Therefore, the number of invalidations will still be the same for the reduced trace and for the original trace.

|                            | 5        |           |           |

|----------------------------|----------|-----------|-----------|

| traces                     | Pero     | Thor      | Pops      |

| original length            | 14,198k  | 16.415k   | 16.087k   |

| reduced trace length       | 641k     | 1.117k    | 1.718k    |

| space reduction            | 22.1     | 14 7      | 94        |

| simu. time for orig. trace | 95.4 sec | 115 9 sec | 118.9 sec |

| simu. time for redu. trace | 5 6 sec  | 10.5 sec  | 15 8 sec  |

| speed-up                   | 17       | 11        | 7.5       |

Table III Time and Space Saving due to Trace Reduction on Simulation of a 4-Processor System

Using the above reduction method Wang (1991) produced reduced traces for the three multiprocessor traces of Table IV. These traces are used to simulate 4-cpu multiprocessor caches, 128 K-byte, direct-mapped with a 4 byte block size. Table III gives the space and time comparison in using long traces vs. reduced traces. It shows that the reduced traces are between 9 to 22 times shorter than the original traces and the simulation times using the reduced traces are between 7 to 17 times shorter.

#### 1.4 Trace Characteristics.

Our traces are on a set of three 4-processor VAX traces and four postprocessed single processor traces as shown in Table IV. These traces were collected by sites and Agarwal (1987). We describe below a summary of these traces. The reader is referred to Sites and Agarwal (1987) for more information about these traces and the post-processing details.

Abaqus is a parallel finite-element analysis program. It is manually decomposed to run on multiple processes, one per CPU, June9 is a batch multiprogramming workload, with no shared data except in the operating system. Cayenne is a parallel version of Spice, a circuit simulation program.

Make is a trace of two X-window network processes plus a disk copy and a make. Pero is a parallel VLSI layout routing program. Thor is a parallel logic simulation program and Pops is a parallel rule-based production system. We use these traces to simulate each individual cache of each CPU in the same way as Sites and Agarwal (1987).

| trace    | # refs | instr | data read | data write | cntxt switches |

|----------|--------|-------|-----------|------------|----------------|

| Pero     | 2840k  | 1812k | 783k      | 245k       | 8              |

| Thor     | 3283k  | 1517k | 1390k     | 376k       | 21             |

| Pops     | 3286k  | 1718k | 1285k     | 283k       | 7              |

| Abaqus   | 1196k  | 514k  | 599k      | 82k        | 292            |

| June9    | 981k   | 550k  | 305k      | 126k       | 230            |

| Cayenne2 | 3483k  | 1599k | 1571k     | 312k       | 892            |

| Make     | 853k   | 402k  | 251k      | 199k       | 16             |

Table IV Characteristics of Traces

## **Chapter Two**

### **Trace Processing**

#### 2.1 Trace Processing: An Overview.

The ultimate objective of trace-driven simulation is, of course, to estimate the performance of a range of memory configurations by simulating their behaviour in response to the memory references contained in an input trace. This final stage of trace-driven simulation is often the most time consuming component because at this level we are often interested in hundreds or thousands of different memory configurations in a given design space. As an example, the space of simple caches defined by sizes ranging from 1 K-bytes to 1024 K-bytes (in powers of two), line sizes ranging from 1 word to 32 words (in powers of two), and associativities ranging from 1-way to 8-way, contains 264 possible design points. Adding the choice of different replacement policies (LRU, FIFO, Random), different set-indexing methods (virtually- or physically-indexed) and different write policies (write-back, write-through) creates thousands of additional possibilities. These design options are for a single cache, but actual memory systems are typically composed of multiple caches that cooperate and interact in a multi-level hierarchy. Because of these interactions different components cannot be considered in isolation. This leads to a further, combinatorial expansion of the design space. Our exploration of the subject material reveals that there are two basic approaches of dealing with this problem:

- Parallel distributed simulations

- Multiconfiguration simulation algorithms.

Since first approach doesn't fulfil the requirements of this project due to some inherent limitations so their discussion is out of scope. Algorithms that enable the simulation of multiple memory configurations in a single pass of an address trace offer another solution to the compute-intensive task of exploring a large design space. We use several criteria to judge a multi-configuration simulation algorithms in this survey. First, it is desirable that the algorithm be able to vary several simulation *parameters* (cache size, line size, associativity, etc.) at a time and, second, that it be able to produce any of several different *metrics* for performance, such as miss counts, miss ratios, misses per instruction (MPI), write backs and cycles per instruction (CPI). The *overhead* of performing a multiconfiguration simulation relative to a single-configuration simulation is also of interest because this value can be used to compute the effective simulation speedup relative to the time that would normally be required by several single-configurations simulations.

#### 2.2 Efficient Cache Simulation Using Multiconfiguration Algorithms.

Almost two decades ago, Mattson (1970) and his colleagues presented an algorithm that can determine the performance (i.e., hit ratios) of all cache sizes under certain replacement policies with only a single pass through the trace file. Their techniques work because the replacement policies they studied guarantee inclusion, the property that, after any sequence of references; the contents of a cache are always a subset of any larger cache. This class of replacement algorithms is called stack algorithms, and the performance evaluation method is therefore known as stack simulation. This stack simulation technique was later extended to cover a wider range of cache organizations TRAIGER, I L., AND SLUTZ, D. R (1991).

The basic idea behind stack simulation is as follows. A common tag stack which holds the reference history is shared by caches of different sizes and with a different number of sets. When a block is requested, a search in the stack is performed until the block is found or the end of the stack is reached. Each element of the stack being visited is compared with the block's tag to determine whether this element is in the same set as the block. This is done for various tag lengths corresponding to the number of sets under study. An array of distance counters is used to keep track of the stack distances for caches with a different number of sets. At the end of the simulation, the distances are used to calculate the hit ratios of interest.

The stack simulation technique works well if the hit ratio is the only parameter of interest. For write-back caches, the frequency of replacing a dirty block is an important parameter since it substantially affects the bus and memory traffic. Unfortunately, this parameter cannot be obtained by using the original technique. This is because a block could be clean for some small caches but dirty for larger ones. Upon replacement, there is no way to tell whether the displaced block needs to be written back to memory. Thompson and Smith's (1989) addressed the write-back frequency problem in the context of fully associative caches. Their method is to attach a dirty level to each block in the stack. This allows them to count the number of writes that can be avoided when the dirty block is still resident in the cache.

Thompson and Smith (1989) were the first to propose efficient simulation algorithms which obtain useful performance measures other than hit ratio, although they considered only fully associative caches. Their technique was extended to a one-pass simulation method for more widely used setassociative write-back caches.

#### 2.3 Stack Algorithms.

Design and research questions regarding memory hierarchies are often investigated with trace-driven simulation of several design alternatives. Mattson et al. (1970) developed the stack simulation technique for simulating many caches with one pass through an address trace. Stack simulation can evaluate alternative caches of many sizes if all have the same number of sets, the same block size, do no prefetching, and use a stack replacement algorithm (e.g., LRU and RANDOM). Caches in a single stack simulation all have different associativities, however, since associativity is cache size in block (which varies in a stack simulation) divided by the number of sets (which is fixed). Design and research questions regarding CPU caches often examine caches of differing sizes, but fixed associativity Smith(1978), Clar(1983), Good(1983), Haik(1984), Hill(1987) and Puzak(1985). Consequently the evaluation of alternative CPU cache designs can require numerous stack simulations.

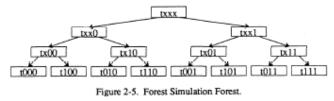

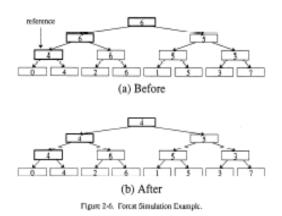

To reduce the number of simulations required, Hill (1987) has developed efficient one-pass trace-driven simulation algorithms for evaluating caches having differing numbers of sets. In some cases he reduces simulation time by using inclusion. He says cache C2 includes cache C1 if cache C2 contains a superset of the blocks in cache C1 after any series of references. A simulation of alternative cache designs can take advantage of inclusion by searching for a reference in cache C1 first, cache C2 second, and then in other caches that include cache C2. When a reference is found, a hit can be reported for that cache and (implicitly) for all caches that include that cache.

Hill (1987) shows when inclusion holds for caches having differing number of sets. He finds inclusion holds between practical direct-mapped (one-way set-associative) CPU caches, but that it does not hold in general between practical set-associative CPU caches. Since direct-mapped caches are important. He develops and algorithm, called forest simulation, for simulating alternative direct-mapped caches that takes advantage of inclusion. He allows alternative caches to use arbitrary functions to map references to sets. He also shows that faster simulation times can be achieved when the functions that map references to sets obey a property called set hierarchy. His algorithm is a generalization of an algorithm for simulating set-associative caches that map references to set with bit selection Mattson(1970), Trai(1971). A cache that uses bit selection contains a power of two number of sets and selects the set of a reference with the least-significant bits of the reference's block number.

Subsequent discussion is based on original work of Hill (1987) and Mattson (1991), and reviews set-associative caches, formally introduces stack algorithms, describes and analyzes linked-list stack simulation and describes more efficient methods of stack simulation.

#### 2.3.1 Set Associative Caches.

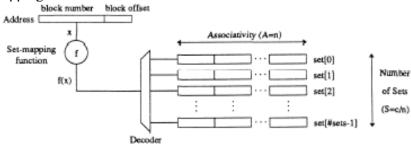

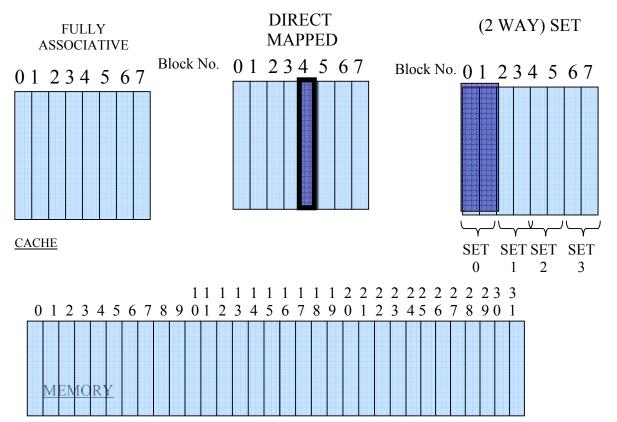

A fully-associative cache allows any block to reside in any block frame. An n-way set-associative cache of c blocks uses a set-mapping function f to partition all blocks in main memory into a number of equivalence classes, and allows at most n blocks from each equivalence class to be simultaneously resident. The block frames that hold blocks from one equivalence class are called a set. The number of block frames in a set, n, is called the associativity (or degree of associativity or set size). The number of equivalence classes in the image of f, called the number of sets, is always equal to c/n, the number of blocks in a cache divided by its associativity. The advantage of a set-associative cache with respect to a fully-associative cache of the same size is that n block frames rather than c block frames must be searched on each reference. The disadvantage of a set-associative cache is that it restricts which blocks can be simultaneously resident. For example, an n-way set-associative cache cannot contain the n + 1 most-recently-referenced block that map to one set. Figure 2-1 illustrates set-associative mapping and discusses Hill's notation for caches.

The most-commonly used set-mapping function is bit selection, because it can be implemented with no logic or delay. In bit selection, several low order bits of the block number are used to select the set. Bit selection requires that the number of sets be a power of two. For example, the set of block x is a cache with 21 sets that uses bit selection is  $f(x) = \text{rem } 2^i$  is the remainder of dividing x by  $2^i$ .

#### 2.3.2. Stack Algorithms: Formal Definition.

The seminal paper on memory hierarchy simulation is Mattson et al. (1970). It introduces stack simulation as an efficient technique for evaluating a series of fully-associative caches and obeys the inclusion property. Since a set-mapping function partitions blocks into equivalence classes and set-associative caches do not allow blocks from different classes to interact, each set of a set-associative cache operates as an independent fully-associative cache. For this reason stack simulation can be applied to set-associative caches that use the same set-mapping function.

Figure 2-1. Set-Associative Mapping.

This figure illustrates set-associative mapping in an n-way setassociative cache of c blocks with set-mapping function f. If a block x is present, it is in one of the n block frames in set f(x) (one row). The number of elements in a single set is the associativity (degree of associativity, set size, A). The number of values in the image of f (number of rows) is the number of sets in the cache (S=c/n). The associativity times the number of sets is always equal to the cache's size in blocks. A cache is direct-mapped if A=1; it is fully-associative if S=1.

*Hill(1987) denotes the above cache with "C(A=n, S=c/n, F=t)."* where A,S and F are cache parameters "associativity." "number of sets" and "set-mapping function". When comparing caches he omits listing parameters

that do not vary. For example, I use "C(A=1)" and "C(A=2)" to contrast a direct-mapped and a two-way set-associative cache that are otherwise similar. When differences are clear, I use subscripts for distinguishing caches (e.g, "C 1", and : $C_2$ "). Finally I use " $c_i$ " (lower case) to represent the number of blocks in cache " $C_i$ " (upper case). Thus " $C_i$ " represents all attributes of cache  $C_i$  while " $c_i$ " represents only the number of blocks in cache  $C_i$ .

Stack simulation is efficient because it takes advantage of inclusion, which is the property that, after any series of references, each larger cache simulated contains a superset of the blocks resident in all smaller caches. Inclusion may seem trivially true, but it is not. For example, a series of caches managed with FIFO (first in first out) replacement do not always obey inclusion. Consider a series of references to blocks 1,2,3,1, and 4. At the end of this sequence, a two-block cache will contain blocks 1 and 4 while a three-block cache will contain 2,3 and 4, but not block 1.

Assuming no perfecting and fixed block size, Mattson et al (1970). show that inclusion holds between caches using the same setmapping function for a class of replacement algorithms called stack algorithms. LRU and RANDOM are the principal, interesting stack algorithms.

A stack simulation of caches C (A=k, F=f) for k = 1 to n uses a stack of n nodes for each set in the image of f, and an array of n distance counters. If we assume LRU replacement, each stack conceptually lists the most-recently-referenced n blocks for its set. Stacks in simulations of other stack replacement algorithms list blocks in order of descending priority, where priorities are defined so that blocks with a lower priority are preferred for replacement with respect to blocks with a higher priority. Each counter distance (k) contains the number reference so far to the k-th most-recently-referenced block. For each reference x, stack simulation performs three steps: *FIND*, *UPDATE and METRIC*.

FIND Locate block x in stack f(x). we say a reference is found at distance k if it is the k-th element in the stack and at distance infinity ( $\infty$  if it not found.

METRIC Increment counters distance [k] and N, where N is the number of reference. At the end of simulation, the miss ratio of cache C (A=k, F=f) is 1-  $j_{=1}\sum^{k}$  distance [k]/N. Metrics can be also be maintained by keeping counters only for specific cache sizes of interest. This will save space, but increase the time required to determine what counter(s) to increment.

UPDATE Update the stack to reflect the contents of all caches after the reference to x. See Mattson et al. (1970). for what is required with an arbitrary stack algorithm. For LRU, x must be moved from it old

position (if any) to the top of stack f(x), all blocks x passes must be moved down one position, and all other blocks must not move, if x was not previously referenced, moved down one position.

#### 2.3.3. Linked-List Stack Simulation.

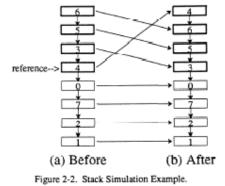

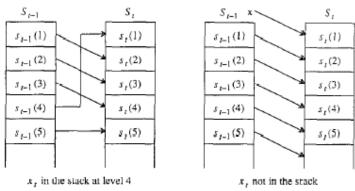

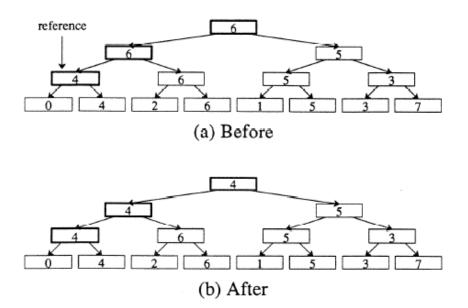

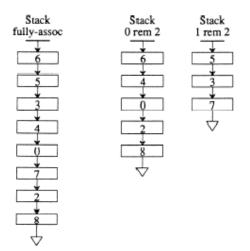

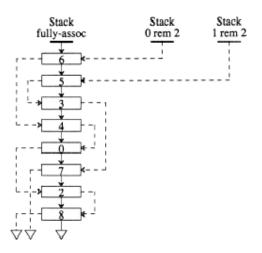

Hill(1987) describes stack simulation with the stack for each set implemented with a linkedlist. This is commonly done for CPU cache simulations, because it is simple to implement and has adequate performance since the referenced block is usually found in the first few elements of the stack. He assumes LRU replacement, because it is commonly used; the arguments that follow can also be extended to other stack replacement algorithms. Figure 2-2 shows an example eightentry stack before and after a reference.

The left stack (a) shows an LRU stack for one sort after a sequences of references to that set, Information in the stack reveals that block 6 is in this set of a direct-mapped cache (one block per set); blocks 6 and 5 are in a two way set-associative cache; blocks 6, 5 and 3 are in a three way cache; ...and blocks 0 through 7 are in an eight way cache. Let the next reference that maps to this set be to block 4. The blocks in bold are examined to find block 4. The search stops when block 4 is found or the stack is exhausted. Since block 4 is located (coincidentally) at stack dept 4, a miss is recorded for all caches smaller than four blocks, and a hit is recorded for all caches 4 blocks or larger. The right stack (b) shows the stack after it has been updated with LRU replacement; the blocks in bold have moved.

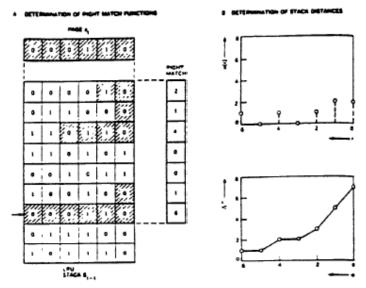

The pseudo-code in Figures 2-3 and 2-4 illustrate the storage and the per-reference processing required by linked list stack simulation. The implementation of FIND (not shown) merely walks down the link-list f(x) until reference x is found or the linked list is exhausted. If x found, the implementation of UPDATE (also not shown) changes two pointers to move x to the head of the linked list f(x). Otherwise, it allocates a new node for x, either from a free list or by reclaiming the last block in the list, and puts the node at the head of the linked list.

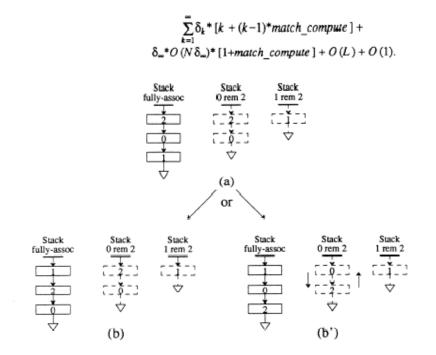

The analysis of the time to simulate each reference is some constant, O(I), that include the time to read the reference, plus the

number of iterations within FIND. Let  $\delta_k$  be the probability that a reference is found at stack depth k, let  $\delta_{\infty}$  be the probability that the reference is not found, i.e this is the first reference to that block, and let N be the number of references in the trace. FIND uses k iterations to find a reference at stack distance k, and  $O(N \delta_{\infty})$  iterations for stack distance  $\infty$  where  $O(N \delta_{\infty})$  is the size of the entire stack. In practice, the average stack size is much smaller than the number of unique blocks in the trace,  $N \delta_{\infty}$ , because the unique blocks are distributed across a 100 or more sets.

```

max assoc .... Maximum stack size

function f (x) – a set-mapping function

integer number of stacks ---- number of sets induced by f (x)

integer N---- number of references

----distance counts so that m (C(F=f,A=k)=1-j=1\sum^{k} distance[j]/N

integer distance (1 max assoc)

define stacknode type {

integer block number

stacknode type next

}

```

stacknode type stack (0: number of stacks-1) --- top of stack pointers ---pool of dynamically linked stacknodes

stacknode type stacknodes (1 number of stacks max assoc)

#### figure 2-3 Stack Simulation Storage

For each reference x (

Read (var x) N + + Stack number = f (x) ---Walk down stack unitl x is found or stack is exhausted. ---If found, return stack distance and pointers to stacknode containing x. ---Otherwise set stack distance to max assoc + 1 and point to LRU stacknode. Found =FIND (x, stack number, var stack distance, Var previous node pointer, var node pointer --METRIC ---if (found) distance (stack distance)++ --If was found, move the stack node of x to the top of its stack. ---Otherwise, store x in LRU stacknode and move it to the top UPDATE(x, stack\_number found, previous node pointer node pointer)

#### **Figure 2-4 Stack Simulation**

The time integer to process a reference is of order:

$$\sum_{k=1}^{\infty} k \, \delta_k + O(N \, \delta_{\infty}) \delta_{\infty} + O(1).$$

The first term, called the mean stack distance, is the average number of distinct blocks since the last reference to the referenced block. If one is simulating only caches with associativity skmax, then no stack node need to be retained beyond distance kmax. This reduces the simulation time to;

$$\sum_{k=1}^{kmax} k \,\delta_k + kmax^* \sum_{k=kmax+1}^{\infty} \delta_k + kmax^* \,\delta_\infty + O(1).$$

Bounding stack size can significantly reduce simulation time of set associative CPU caches, where kmax rarely exceeds eight. However, for fully associative caches, kmax is equal to the number of block in the largest cache simulated. The run-time of linked list stack simulation of fully associative caches will be poor if either  $_{k=kmax+1}\sum^{\infty} \delta_k$  or  $\delta_{\infty}$  is large.

An analysis of the exact storage required for bounded linked list stack simulation of even large CPU caches is uninteresting, because the storage required is small relative to modern main memories. For example, the storage required by the linked list stack simulation pseudo code in figure 2-3 for simulating a direct mapped 128K-btye cache, a two way set associative 256 K byte cache, a four way512 K cache and eight way 1M cache with 32 byte blocks is approximately equal to the number of blocks in the 1M byte cache (32K) times 8 bytes per block, and is less than 300 K bytes.

#### 2.3.4 Other Stack Simulation Implementation.

Bennett and Kruskal(1975) examine the paging behaviour of a large data base. They find mean stack distances of 1 to 328 entries for varying page sizes. Bennett and Kruskal propose an algorithm for stack simulation using an m-ary tree and a hash table where the run time per reference is approximately logarithmic in the number of block since the last reference to the current block. In contrast, the time per reference for linked list stack simulation is linear in the number of distinct blocks since the last reference of the current block. Bennett and Kruskal conclude that their algorithm is of order ten times faster than linked list stack simulation for mean stack distances of 150 entries. The storage requirements of the algorithm are large, but this is not important since the memory required is small relative to modern main memory sizes. The tree size is linear in the length of the address trace, N, and the hash table must be larger than the number of distinct blocks (N  $\delta_{\infty}$ ). A simulation of 10 million references with 200.000 unique blocks requires only 3M bytes of storage if it uses two bits per reference and two words per unique block. Olken (1981) changes Bennett and Kruskal's algorithm by replacing their m-ary tree with an AVL tree.