## ABSTRACT

In today's world of advanced Internet, mobility is a key service. The use of smart phones, tablets and wearable devices is on the rise at fast pace. However, traditional software-based security solutions are unable to deliver the satisfactory level of protection and security assurances to the mobile device users especially in enterprise, government and military. In recent past, mobile industry has made efforts to standardize the security specifications. The standards from National Institute of Science and Technology (NIST) and Trusted computing Group (TCG); Trusted Platform Module (TPM) 1.2, Trusted Platform Module 2.0 and Mobile Trusted Module; have been analyzed and found that software based mobile security standards are unable to provide the basis of strong foundation required to implement mobile security as compared to the hardware rooted security mechanisms. Therefore, the standards for mobile devices need to be revised to overcome the inherit shortcomings. It was found that majority of the mobile security solutions were based on ARM System-on-Chip (SoC) that offer TrustZone security architecture with the vendors' specific solutions mounted on it. The integrated solution of ARM TrustZone does not comply with the available standards, and hence, several security vulnerabilities have also been reported. As all the hardware rooted security solutions are vendor specific, closed form and non-standardized a new mobile security model mobile Trusted Platform Module (mTPM) has been proposed. An effort has been done to comprehensively cover conceptual framework over existing standards and their corresponding implementation methodology. mTPM suggests the hardware rooted security implementation technique on the existing ARM TrustZone security technology while overcoming its shortcoming especially pertaining to lack of secure hardware peripherals including establishing the integrity of various roots of trust for processing, storage, entropy source, clock, and access to firmware. Fundamentally it could be considered as embedding a TPM hardware device in ARM SoC by suitable augmenting the existing architecture with additional hardware and software resources. It is hoped that the proposed mTPM model will provide a unified, vendor neutral and standardized security platform for the mobile device manufacturers. However, it is felt that the whole

concept should be subjected to physical testing and evaluation on a test bed through fabrication of prototype SoC.

## **DECLARATION**

I hereby declare that no portion of work presented in this thesis has been submitted in support of another award or qualification either at this institution or elsewhere.

(Naveeda Ashraf)

## ACKNOWLEDGMENTS

All praises to Allah for the strengths and His blessing in completing this thesis.

I would like to convey my gratitude to my supervisor, Dr. Rabia Latif, for her supervision and constant support. Her invaluable help of constructive comments and suggestions throughout the experimental and thesis works are major contributions to the success of this research.

I would also like to express my sincerest appreciation to Lec Waleed Bin Shahid and Lec Narmeen Shafqat for being an important part of my Research Supervisory Committee. Their scholarly guidance, assistance and knowledge have been meaningful for successful completion of my research.

I extend my deepest gratefulness to my father, Dr. Ashraf Masood, who provided me a platform and gave me the liberty to work in the area of my interest and extended his tremendous support prior to as well as during the course of this research. His technical guidance, encouragement, ideas and perspective were vital for completion of this tedious task. His support gave me confidence and helped me to understand about the subject matters deeply and inspired me towards my goals.

Last, but not the least, I am highly thankful to my mother (Mrs. Perveen Ashraf), my husband (Mr. Zeeshan Siddique) and my parents-in-law. They have always stood by my dreams and aspirations and have been a great source of inspiration for me. I would like to thank them for all their care, love and support through my times of stress and excitement.

Finally, I am grateful and thankful to Military College of Signals and National University of Sciences and Technology for providing me a chance to help achieve excellence by being associated with the prestigious institutions.

# **TABLE OF CONTENTS**

| Abs  | stract                                    | iv                                                        |  |

|------|-------------------------------------------|-----------------------------------------------------------|--|

| Dec  | laration                                  | vi                                                        |  |

| Ack  | nowledg                                   | gments vii                                                |  |

| Tab  | ole of Co                                 | ntents viii                                               |  |

| List | t of Figu                                 | res xii                                                   |  |

| List | t of Tabl                                 | es xiv                                                    |  |

| Abb  | oreviatio                                 | ons Xv                                                    |  |

| СН   | APTER                                     | 1 - Introduction                                          |  |

| 1.1  | Introc                                    | luction1                                                  |  |

| 1.2  | Probl                                     | em Statement                                              |  |

| 1.3  | Resea                                     | arch Objective                                            |  |

| 1.4  | Resea                                     | arch Methodology                                          |  |

| 1.5  | .5 Significance for Industry and Military |                                                           |  |

| 1.6  | .6 Thesis Contribution                    |                                                           |  |

| 1.7  | Thesi                                     | s Organization                                            |  |

| 1.8  | Conc                                      | lusion7                                                   |  |

| СН   | APTER                                     | 2 - Hardware Rooted Security Standards And Their Analysis |  |

| 2.1  | Introc                                    | luction                                                   |  |

| 2.2  | NIST                                      | Hardware Rooted Security Architecture                     |  |

|      | 2.2.1                                     | Trusted Security Components                               |  |

|      | 2.2.2                                     | Key Security Capabilities                                 |  |

|      | 2.2.3                                     | Mobile Device Security Architecture                       |  |

| 2.3  | TPM                                       | MOBILE Specifications                                     |  |

|      | 2.3.1                                     | TPM Specifications                                        |  |

|      | 2.3.2                                     | Mobile Trusted Module                                     |  |

|      | 2.3.3                                     | The GlobalPlatform TEE17                                  |  |

| 2.4  | TPM                                       | MOBILE Security Model                                     |  |

| 2.5 | Anal   | ysis of Standrads                                               | 21 |

|-----|--------|-----------------------------------------------------------------|----|

|     | 2.5.1  | Comparative Analysis of Standards                               | 22 |

|     | 2.5.2  | Analysis of MTM Specifications                                  | 23 |

| 2.6 | Selec  | tion of Cryptographic Algorithms                                | 25 |

|     | 2.2.1  | Lightweight Block Ciphers                                       | 25 |

|     | 2.2.2  | Lightweight Hash Functions                                      | 28 |

| 2.7 | Conc   | lusion                                                          | 30 |

| СН  | APTER  | 3 – Mobile Security Implementation Solutions And Their Analysis | 31 |

| 3.1 | Intro  | duction                                                         | 31 |

| 3.2 | Intern | nal Components of a TPM                                         | 31 |

|     | 3.2.1  | Secured Input and Output                                        | 31 |

|     | 3.2.2  | Cryptographic Processor                                         | 32 |

|     | 3.2.3  | Non Volatile and Volatile Memory                                | 33 |

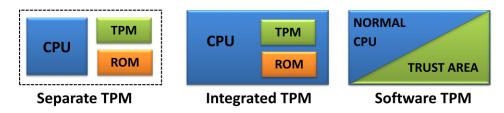

| 3.3 | TPM    | Implementation Techniques                                       | 33 |

|     | 3.3.1  | Separately Mounted TPM                                          | 34 |

|     | 3.3.2  | Software TPM                                                    | 34 |

|     | 3.3.3  | Integrated TPM                                                  | 34 |

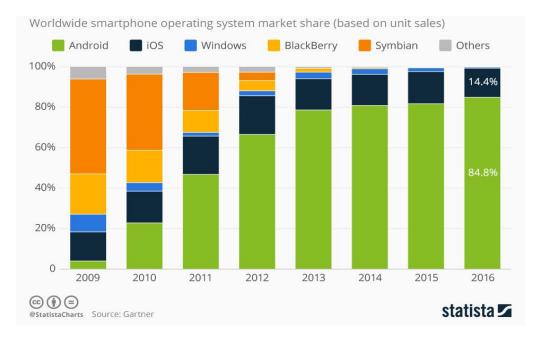

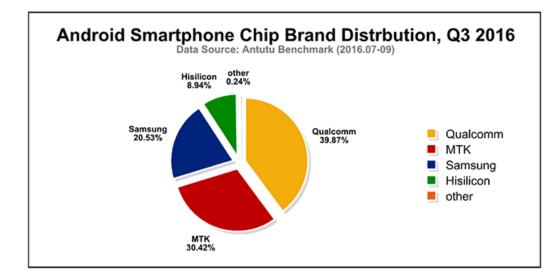

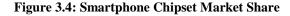

| 3.4 | Mobi   | le Market Share Analysis                                        | 35 |

| 3.5 | Conte  | emparary Implementation Solutions                               | 36 |

|     | 3.5.1  | ARM TrustZone                                                   | 37 |

|     | 3.5.2  | Qualcomm                                                        | 38 |

|     | 3.5.3  | Samsung                                                         | 39 |

|     | 3.5.4  | MediaTek                                                        | 39 |

|     | 3.5.5  | Intel                                                           | 40 |

|     | 3.5.6  | Boeing                                                          | 40 |

|     | 3.5.7  | Apple                                                           | 40 |

| 3.6 | Analy  | ysis of Market Implementation Solutions                         | 42 |

| 3.7 | ARM    | I TrustZone Architecture                                        | 42 |

|     | 3.7.1  | Processor Architecture                                          |    |

|     | 3.7.2  | Memory Architecture                                             | 45 |

|     | 3.7.3  | Software Architecture                                           | 45 |

|      | 3.7.4   | Booing a Secure System                                            | 45 |

|------|---------|-------------------------------------------------------------------|----|

|      | 3.7.5   | TrustZone API                                                     | 47 |

| 3.8  | Andr    | oid Exploit Database                                              | 49 |

| 3.9  | Short   | comings of ARM TrustZone                                          | 52 |

|      | 3.9.1   | Absence of Secure Storage                                         | 52 |

|      | 3.9.2   | Absence of Secure Clock                                           | 52 |

|      | 3.9.3   | Lack of Secure Entropy and Persistant Counter                     | 53 |

|      | 3.9.4   | Security Provided Through Virtualization Technique                | 53 |

| 3.10 | ) Com   | bliance of ARM TrustZone with Standards                           | 53 |

| 3.11 | Conc    | lusions                                                           | 54 |

| CH   | APTER   | 4 - mTPM: Proposed Security Model For Mobile Devices              | 55 |

| 4.1  | Intro   | luction                                                           | 55 |

| 4.2  | Revie   | ew of Conclusions of Analytical Results                           | 55 |

| 4.3  | Propo   | osed Security Model - mTPM                                        | 56 |

|      | 4.3.1   | Suggested Modifications in Standard and mTPM                      | 57 |

|      | 4.3.2   | Proposed Implementation Solution for mTPM                         | 59 |

| 4.4  | Acce    | ssing Secure Resources from OS and Applications                   | 65 |

| 4.5  | Conc    | lusion                                                            | 68 |

| CH   | APTER   | 5 – Proposed mTPM: Discussion and Analysis                        | 69 |

| 5.1  | Intro   | luction                                                           | 69 |

| 5.2  | Sumr    | nary of the Architectural Specifications of mTPM                  | 69 |

| 5.3  | mTPI    | M – Proposed Model Implementation Feasibility                     | 70 |

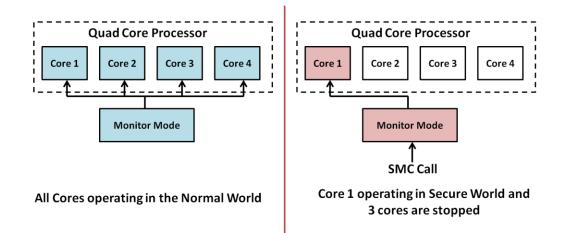

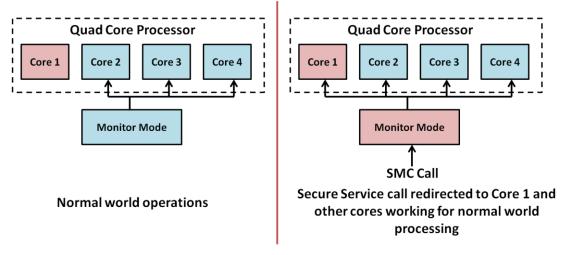

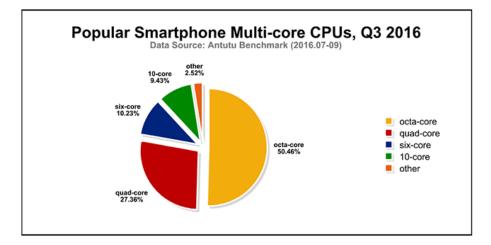

|      | 5.3.1   | Implementation on Multi-core Processors                           | 70 |

|      | 5.3.2   | Dedicating Secure functions to a Single Core                      | 71 |

|      | 5.3.3   | Dedicating Secure Memory to Secure Functions                      | 72 |

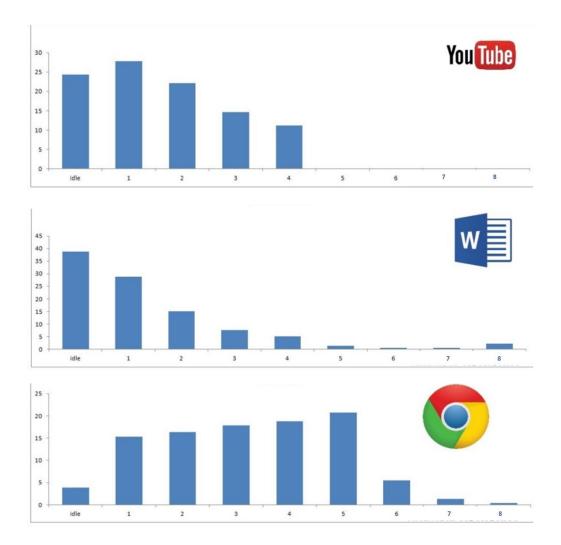

|      | 5.3.4   | Percentage Usage of a Core in a Multi-core Processor Architecture | 73 |

| 5.4  | mTP     | M Compliance with Standards                                       | 75 |

| 5.5  | Adva    | ntages of the Proposed mTPM Model                                 | 78 |

| 5.6  | Conc    | lusion                                                            | 79 |

| Con  | clusion | 5                                                                 | 81 |

| Future Work | . 84 |

|-------------|------|

| References  | . 86 |

# LIST OF FIGURES

| Figure 1.1: Research Methodology                                             | 1 |

|------------------------------------------------------------------------------|---|

| Figure 2.1: NIST's Mobile Device Architecture                                | 3 |

| Figure 2.2: Generic Architecture of MTM 16                                   | 5 |

| Figure 2.3: TPM MOBILE Boot Process                                          | 3 |

| Figure 2.4: Mobile Device Protection Hierarchy                               | ) |

| Figure 2.5: Platform Integrity in TPM Mobile Security Model                  | ) |

| Figure 2.6: Secure Storage in TPM Mobile Security Model 20                   | ) |

| Figure 2.7: Isolation Execution in TPM Mobile Security Model                 | 1 |

| Figure 2.8: Mapping of RoT's For Security Capabilities                       | 2 |

| Figure 2.9: Comparative Analysis of Throughput of Popular Lightweight        |   |

| Block Cipher                                                                 | 5 |

| Figure 2.10: Comparative Analysis of RAM Utilization of Popular Lightweight  |   |

| Block Cipher                                                                 | 7 |

| Figure 2.11: Analysis of ROM Utilization of Popular Lightweight Block Cipher | 3 |

| Figure 2.12: Comparative Analysis of RAM Utilization of lightweight Hash     |   |

| Functions                                                                    | ) |

| Figure 3.1: Internal Component of a TPM Chip                                 | 2 |

| Figure 3.2: Options for Implementing TPM Functionality                       | 3 |

| Figure 3.3: Yearly Smartphone OS Market Share                                | 5 |

| Figure 3.4: Smartphone Chipset Market Share                                  | 5 |

| Figure 3.5: Android Smartphone Chipset Market Share                          | 5 |

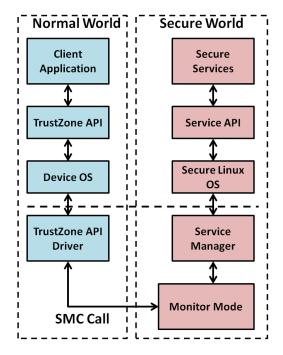

| Figure 3.6: ARM Trust-Zone Environment                                       | 7 |

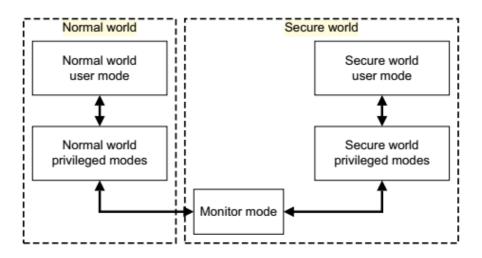

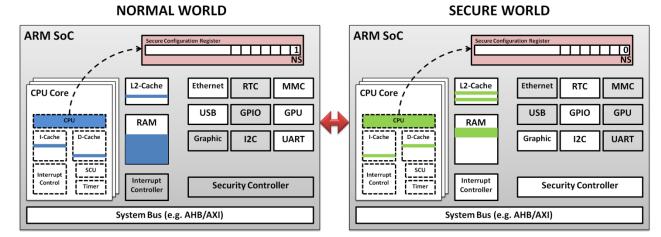

| Figure 3.7: ARM TrustZone Virtual Modes Implementing Security Extensitons    | 1 |

| Figure 3.8: Switching Mechanism from Normal world to Secure world            | 5 |

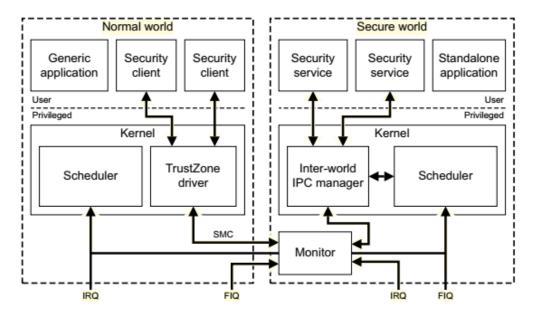

| Figure 3.9: Software Architecture of ARM TrustZone 46                        | 5 |

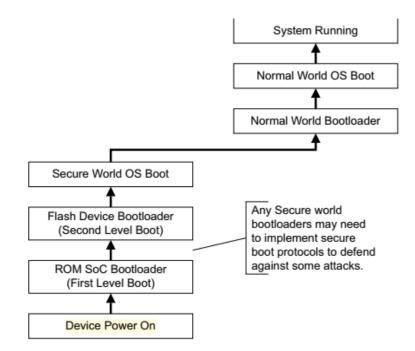

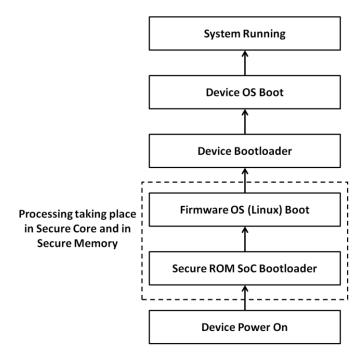

| Figure 3.10: A typical boot sequence of an ARM TrustZone based processor     | 7 |

| Figure 3.11: ARM TrustZone Access Mechanism                                  | ) |

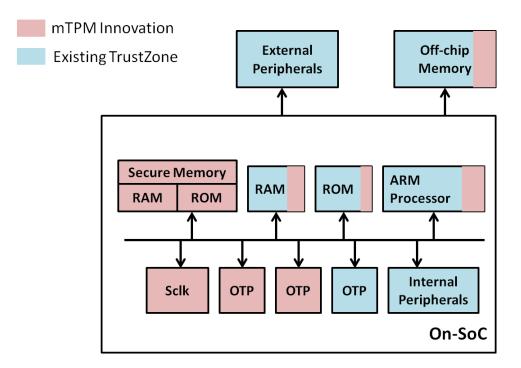

| Figure 4.1: mTPM and TrustZone combined SoC Components                       | 3 |

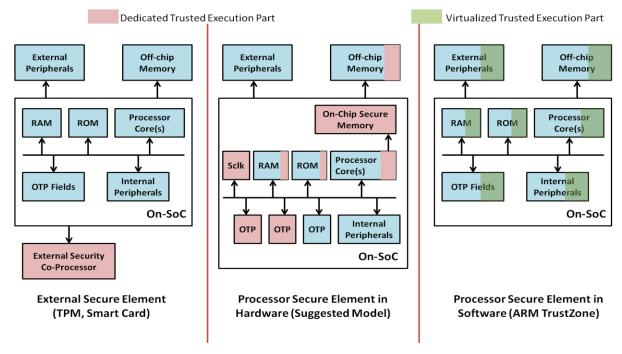

| Figure 4.2: TEE Hardware Realization Alternatives                                | 65 |

|----------------------------------------------------------------------------------|----|

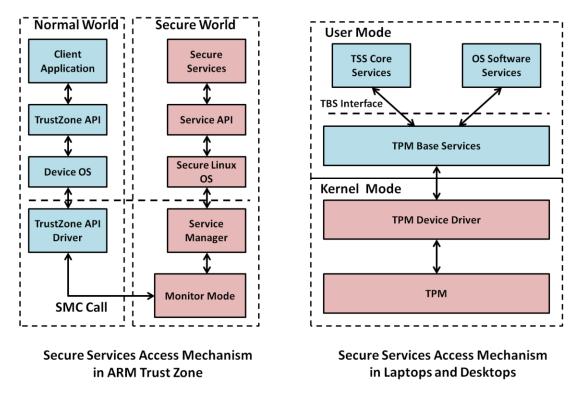

| Figure 4.3: Secure Services Access Mechanism                                     | 66 |

| Figure 4.4: ARM TrustZone Secure Service Execution Mechanism                     | 67 |

| Figure 4.5: Proposed Model Security Operation Access Mechanism                   | 67 |

| Figure 5.1:Market Share of Multi-core Processors                                 | 71 |

| Figure 5.2: Percentage of time the numbers of cores are being used in processing | 74 |

| Figure 5.3: Secure Boot in the Proposed Model                                    | 77 |

| Figure 5.4: ARM TrustZone Secure Service Execution Mechanism                     | 67 |

| Figure 5.5: Proposed Model Security Operation Access Mechanism                   | 67 |

# **ABBREVIATIONS**

| API  | Application Programming Interface            |

|------|----------------------------------------------|

| BYOD | Bring Your Own Device                        |

| BBS  | Blum Blum Shub                               |

| DRM  | Digital Management Rights                    |

| EH   | Endorsement Hierarchy                        |

| IoT  | Internet of Things                           |

| MDM  | Mobile Device Management                     |

| MTM  | Mobile Trusted Module                        |

| NIST | National Institute of Science and Technology |

| NH   | Null Hierarchy                               |

| PEE  | Policy Enforcement Engine                    |

| PH   | Platform Hierarchy                           |

| ROT  | Root of Trust                                |

| RNG  | Random Number Generator                      |

| ROTI | Root of Trust of Integrity                   |

| ROTM | Root of Trust of Measurement                 |

| ROTR | Root of Trust of Reporting                   |

| ROTS | Root of Trust of Storage                     |

| ROTV | Root of Trust of Verification                |

| RPMB | Replay Protected Memory Block                |

| RTC  | Real Time Clock                              |

| Sclk | Secure Clock                                 |

| SCR  | Secure Configuration Register                |

| SES  | Secure Entropy Source                        |

| SH   | Storage Hierarchy                            |

| SMC  | Secure Monitor Call                          |

| SoC  | System on Chip                               |

| TBS  | Trusted Base Services                        |

| TCG   | Trusted Computing Group                     |

|-------|---------------------------------------------|

| TEE   | Trusted Execution Environment               |

| TPM   | Trusted Platform Module                     |

| TRNG  | True Random Number Generator                |

| TZAPI | TrustZone Application Programming Interface |

|       |                                             |

## Chapter 1

## INTRODUCTION

## 1.1 Introduction

Since the birth of mankind efforts had been made to invent devices which help in computing. The first known tool was abacus invented for the arithmetic tasks by the Babylon early in 2400 B.C. As the time passed technology enhanced and Charles Babbage invented the first mechanical computer in 19<sup>th</sup> century and originated the concept of programmable computer. In the first quarter of 20<sup>th</sup> century various sophisticated analog computers were made using direct mechanical or electrical model for computation. In 1944 the first electronic digital programmable computer was made named Colossus used by the Germans in World War 2. The concept of modern computing was given by Alan Turning in 1936. Since then technology advancements took place and vacuum tubes were replaced by transistors and then integrated circuits. With the invention of integrated circuits a revolution took place in the computing market and the first desktop computer was invented in 1971 named KENBAK-1. With the persistent miniaturization of computing resources and improvement in portable battery life, portable computers grew into popularity in last decade of 20<sup>th</sup> century. The need of portable computing encouraged the manufacturers to integrate the computing resources into cellular phones and now in different wearable and IoT.

With the increased pace in the development of computing devices the need to secure the computational data also increased. In 2003 Trusted Computing Group (TCG) took the first step to standardize the security implementation and gave the specifications for a Trusted Platform Module (TPM). In 2006 the computers were started to introduce the embedded TPM chips and built in security. Since then the standards as well as computing devices were modified with the time with enhanced security assurances to provide the security capabilities of confidentiality, integrity and availability. The question of security became complex when networking came into existence and it became even worse with the introduction of mobile computing.

As dependence on mobile technology is increasing, the employees tend to use personally-owned and organization-issued mobile devices simultaneously to utilize corporate data, resources and services for perform different activities. But unfortunately, mostly theses mobile devices especially personally owned are unable to provide strong security assurances to the organizations and end users. Besides the laptops and other such devices provide a hardware rooted security which lack in present mobile devices. Rooting and jail breaking are the common vulnerabilities present in mobile devices, which although provide the device users with greater flexibility and control over the devices but also bypass important security features and thereby introduce more threats and vulnerabilities. Enterprises have to accept these security risks present in the mobile devices because of several factors which include cost savings and employee desire for greater convenience.

The analysis of mobile attacks has cleared the importance of hardware based security. Some of the observations are based on the fact that security solutions are implemented most often in software. Also, the increasingly popular use of virtualization technologies to manage security in isolated environments or the software-based security offered through anti-virus or anti-theft applications are not able to prevent waves of advanced persistent attacks and thus security has to live underneath the operating system and be further assisted by the system hardware

With the increased utilization of smart connected devices mainly tablets and mobile phones, have fundamentally transformed our life styles where we now can access personal networks, bank accounts and business documents wherever and whenever required. In order to take full benefit of the richness and connectivity of these devices, there is a need to control the associated risks. This need activated to emerge one key platform Trusted Computing Group's Mobile Trusted Module with the other key platform Global Platform's Trusted Execution Environment. These two technologies work together in a unified manner called TPM MOBILE to provide security, peace of mind and enhanced services to its consumers. In 2012 NIST published SP 800-164 and took the step to standardize the basic requirements to harden the core of mobile devices. Hence all mobile devices should meet these standards as a primitive.

Although implementing good security hygiene and security tools provide efficiency and security and are a vital part of organization's security policy, even the best practices can be bypassed as users always remain the most commonly leveraged attack vector. Mobile industry is working to implement measures that "harden" the mobile devices, and embedding security into the core of mobile devices. Some of the leading solutions provided by different companies in the area of hardening include Qualcomm, Intel, Samsung Knox, Apple and Boeing. All the vendors provide their own closed form solutions based upon ARM Trust Zone security technology

The use of smart phones, tablets and wearable devices is on the rise at fast pace in enterprise, government and military. However, traditional software-based security solutions are unable to deliver the satisfactory level of protection and security assurances to the mobile device users. Higher level of security for such applications can only be ensured through hardware mechanisms. This research will focus on securing the mobile device through hardware rooted security and adaptation into such low power and resource constraint devices. Moreover, based on improved standards and practically feasible implementation technology, a hardware security solution will also be proposed for Android smart phones.

## **1.2 Problem Statement**

In context to the above discussion the security of the mobile devices is not fool proof due to the following reasons:

- The software of mobile devices including its operating system is vulnerable to penetration by the attackers

- Hardware solutions proposed or implemented till date are non-compliant to standards, ad-hoc, vendor specific and closed form solutions.

## **1.3 Research Objective**

The main objective of this thesis was:

• Analyze various Trusted Platform Module (TPM) standards and specifications available for security in desktop, laptops and other computing devices for adoption as primitives of MTM.

- Carry out a survey to analyze the extent of success of commercial implementation of MTM in android based mobile device by various vendors.

- Propose a hardware security solution based on improved standards and practically feasible implementation technology.

## **1.4 Research Methodology**

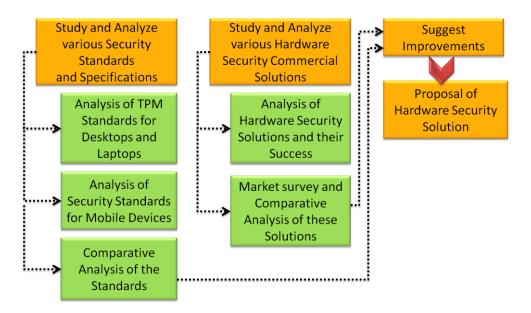

Figure 1.1 illustrates the research methodology which will be adopted during the research work.

Figure 1.1: Research Methodology

The research will be started with the analysis of security standards available. This will include the analysis of the standards employed in static computing devices such as laptops and desktops. Afterwards the mobile security standards will be analyzed. This will include the understanding of NIST standards and the TCG standards. Afterwards a comparative analysis of all these standards will be carried out. Moreover the limitations present in standard will also be notified.

The second part of research will be to analyze the available commercial solutions. This will include the study and analysis of the hardware rooted security commercial solutions and the extent to which they comply with the standards. Afterwards a comparative analysis of these solutions will be carried out and the limitations in their security implementation strategy will be notified.

The third part of research will be to propose improvements in the standards limitations. Also a practically implementable hardware security solution will be proposed based on the improved standards and specifications.

## **1.5** Significance for Industry and Military

Use of mobile devices by the military, diplomatic and other security agencies has increased rapidly since the last decade. In the absence of standardized solution, customized products with ad-hoc security system implementation are usually deployed. However, these devices are neither cost effective nor provide the necessary security assurances for military organizations and miss the requisite layer of security and ruggedized hardware to optimize it required for military purposes. Hence the proposed solution will discriminate itself from the available solutions by providing a standardized, vendor neutral, low cost and low power solution with reduced die size which are the main security constraints while incorporating hardware rooted security in mobile devices.

## **1.6** Thesis Contribution

It is said to the best of our knowledge that proposed model has not been published in any paper and is solely presented after our own research. Moreover the analysis and limitations of standards and ARM TrustZone mentioned during has not been done previously in any research studies.

The contribution of thesis in academics and industry will be as follows;

- In academics it will contribute towards the documented detailed analysis of the hardware rooted mobile security standards and their comparative analysis. Furthermore the documented analysis of the commercial solutions and their analysis will be a great add on and help for other researchers. Moreover the detailed analysis carried out for ARM TrustZone and its limitations will contribute towards boosting more research solutions for the industry.

- In industry it will contribute towards the analysis of different solutions and the extent to which they comply with the available standards. Moreover it will boost

the industry to modify the current standards based on the limitation notified during the thesis. The proposed solution will provide all the manufacturers with a unified and standardized security platform to build their secure mobile devices making the solutions vendor neutral. Moreover the proposed solution will facilitate the developers as the security solution is complete as a whole and is an open source solution.

- A survey paper on the topic "Analytical Study of Hardware-Rooted Security Standards and its Implementation Techniques in Mobile Devices", has also been accepted in 6<sup>th</sup> "International Conference On Identification, Information And Knowledge In The Internet Of Things (IIKI)", held in Qufu, China on 20-22 October217. IIKI 2017, is the sixth conference in the series which provides a dedicated forum for international experts to discuss current trends, challenges, and state-of-the-art solutions in the Internet of Things.

- A regular paper on the topic "Analytical Study of Hardware-Rooted Security Standards and its Implementation Techniques in Mobile Devices", has also been accepted in the 15<sup>th</sup> International Conference on Information Technology - New Generations (ITNG), being held in Nevada, Las Vegas, USA on 16-18 April 2018

## 1.7 Thesis Organization

The thesis is structured as follows:

- **Chapter 2** discusses different hardware rooted security standards available to the industry to develop secure mobile devices. The comparative analysis of these standards is carried out and the shortcomings present in them have been reported.

- Chapter 3 discusses the key components of a TPM and its implementation techniques. Moreover different commercial solutions have been discussed in this chapter. The ARM TrustZone architecture is analyzed deeply and how different security components and mechanisms are deployed in it. Moreover the shortcomings analyzed in the ARM TrustZone are which are supported by the list of exploits of TrustZone gathered different internet sources.

- Chapter 4 suggests the proposed hardware rooted security solution. It consists of two parts. First is the suggested modification of the limitations in the mobile standards. Second is the suggested security model which is based on the modifications in the shortcomings of ARM TrustZone security model. Some more enhancements to implement the modifications are also the part of this chapter.

- **Chapter 5** discusses the implementation mechanism and feasibility of the proposed hardware rooted security model mTPM. Moreover it also analysis the model for the compliance with the existing and modified standard and will carry out a comparative analysis of the security features inherit in ARM Trust Zone and proposed mTPM.

- **Conclusion** will summarize the whole research work and will notify the conclusions drawn during the thesis.

- **Future work** will end the thesis while highlighting the academic and industrial importance and more research directions in accordance to this thesis.

## 1.8 Conclusion

The objective and motivation to conduct the research on hardware rooted security in mobile devices has been described in this chapter. The research methodology developed during the research is also mentioned. Its importance for academics, industry and military has also been highlighted. At the end it describes the overall structural organization of the thesis.

# HARDWARE ROOTED SECURITY STANDARDS AND THEIR ANALYSIS

## 2.1 Introduction

In today's world of advanced internet, mobility is a key service. Therefore, mobile devices, such as smart phones and tablets, should support primary security objectives; confidentiality, integrity, and availability such that the mobile devices are secured against variety of the new and advanced threats. The laptops and other such devices provide a hardware-rooted security which is now expected to be available in the current mobile devices such as smart phones, tablets and various types of wearable.

To provide the baseline for hardware rooted security architecture in mobile devices some standards were developed. Hence in this chapter we will discuss different security standards developed for the mobile security purpose and their analysis will be carried out. Firstly we will discuss the standard developed by NIST. Afterwards the specifications given by TCG for laptops and mobile security platform will be highlighted. The TPM MOBILE security model will be discussed in detail. The chapter will end with the analysis of the available security model.

## 2.2 NIST Hardware Rooted Security Architecture

The previous discussion has cleared the importance of the requirement of hardware security in mobile devices. But many mobile devices are deficient in built-in secure hardware roots of trust. In 2012 NIST published SP 800-164 and took the step to standardize the basic requirements to harden the core of mobile devices. This section will in detail explain the NIST's hardware rooted security architecture. [3]

#### 2.2.1 Trusted Security Components:

According to NIST the following three trusted core components should be developed in the mobile devices to form a hardware rooted security mobile device. Verification of the set of security components to provide security capabilities for personal and bring your own device (BYOD) or company-issued device is required. These security components are:

#### 1. Roots of Trust (ROT):

ROTs provide the foundation of trust assurance on the mobile devices. These ROTs can be deployed in hardware, software or firmware to provide the set of the trusted security critical functions. Hardware ROTs have more reliable behavior as compared to software ROTs and provide better immutability and smaller attack surfaces. Beside, software ROTs offer the advantage of fast deployment on diverse platforms. ROTs are trusted to perform such security-critical functions as software verification, cryptographic key protection, device integrity and device authentication, and behave in a trusted and predictable manner because their error cannot be identified. They are expected to discourage or prevent hackers from accessing the firmware when a mobile device is powered on. They also provide an evidence for hardware security foundation for Trusted Execution Environments (TEEs). Each ROT can be graded and evaluated according to the level of security it has to provide to the system. The devices should implement the following ROTs specified by NIST guidelines to provide the key security capabilities in the mobile devices:

#### • Root of Trust for Storage (ROTS):

There should be a secure interface and repository to manage and store the cryptographic keys and other critical security parameters including the processing of policy details. It is preferred to implement ROTS in hardware as it should typically contain the cryptographic capabilities and keys which are used by the ROTS which are confined to its own logical boundary and not allowed to be accessed in plaintext by any other part of the system.

#### • Root of Trust for Verification (ROTV):

A secure interface or engine should be present for digital signatures verification of all the applications and mechanisms and generate assertions according to the outcome. It also executes the algorithms of signature verification and accesses the key store to verify the digital signatures. The keys may be stored in the internal memory of ROTV or it may request ROTS for the services.

#### • Root of Trust for Integrity (ROTI):

NIST has identified this new ROT for integrity, which was not previously present in other standards. The device should provide an isolated secure interface, secure storage and integrity protection to store and manage the assertions. Tamper resistant locations are present to securely store the measurements and its assertions. The protected interface and the tamper resistant locations together form the ROTI.

#### • Root of Trust for Reporting (ROTR):

This ROT provides a secure environment and interface to generate device integrity reports by identifying, managing and signing the assertions. It supplies the information after binding it cryptographically with its entity. ROTR provides the capability of integrity and non-repudiation of the device integrity reports.

#### • Root of Trust for Measurement (ROTM):

ROTM offers trusted measurement functionality that is used by the assertions, attested by ROTR and protected via ROTI. It has the ability of reliable integrity measurements and establishes a ROT chain of transitive measurement components. The later the ROTM is called, the more the adversary gains the opportunity to weaken the measurement trust chain.

#### 2. Application Programming Interface (API):

The API's expose the ROT's to the platforms so that OS and applications can have high level of security assurance. Mobile OS use the features offered by the ROTs to generate and store device integrity reports, measure and verify software and firmware, and protect locally stored authentication credentials, cryptographic keys and various sensitive data. This interface offers the professionals a set of security features which will secure their applications and protect their processing data. The layer of APIs reduces the burden on application developer to utilize the security trusted components of the ROTs and the OS without bothering about how to implement low level security features. Hence the APIs should be standardized for the mobile devices to bring all the developers on a unified platform and to use these security capabilities across a broad range of devices. Applications request the APIs for the ROTs services of data protection through encryption, device integrity reports and to store or recover authentication credentials and other similar data.

#### 3. The Policy Enforcement Engine (PEE):

PEE is generally the part of mobile OS. It imposes policies on the device in accordance with other device components and allows maintenance, management and processing of policies on both the Information Owner's and device environments. The PEE offers the Information Owners with the capability of control over their information. The PEE makes the policies based on the Information Owners requirements and enforce them while sharing information and storing within the device and across network. In the case of an un-resolvable conflict this engine notifies the device owner and enforces a default policy which denies the unauthorized access of data until the error is resolved.

#### 2.2.2 Key Security Capabilities:

In order to meet the NIST criterion the mobile devices should implement the following three key data security capabilities:

#### **1. Device Integrity:**

Device integrity refers to the nonexistence of corruption in the hardware, software or firmware of a device. A mobile device provides an evidence of secure execution and device integrity if its configurations can be shown to be in a trusted state. Counterfeited devices will not connect, store data or run applications.

#### 2. Isolation:

Isolation refers to the ability of the system to keep different data components, applications and mechanisms separate from each other and hence control the flow of information from one process to another. In mobile devices isolation is required between different layers of architectural contexts and assurance that no applications interfere in the process of other application. The isolation mechanisms make use of the assertions generated by the ROTs to establish the required secure environment.

#### **3. Storage Protection:**

Storage protection refers to preserve the confidentiality and integrity of data at rest and in transit and upon access revocation. Protected storage primarily depends on encryption algorithms used to authenticate credentials of authorized users for integrity and protection of data and the associated keys. The most prominent risks offered while establishing secure storage include exposure of the secure keys in an insecure domain or insecure storage of those keys. The keys must also be stored securely during and after processing of encryption or decryption algorithms, integrity protection and digital verification algorithms. It should be standardized practice of the application developers to request the services of RTS to use and store the encryption keys. Protected storage and key protection mechanisms collectively ensure secure authorization for retrieval of keys and minimize exposure of keys to unsecure area. Protected storage also provides confidentiality and integrity of data by cryptographic means and controlling the access of unauthorized users, processes or devices through logical or physical means. Physical protection includes restricted access of keys by authorized entities to permitted operations. Logical protections include access policies implemented in firmware or software permitting authorized access.

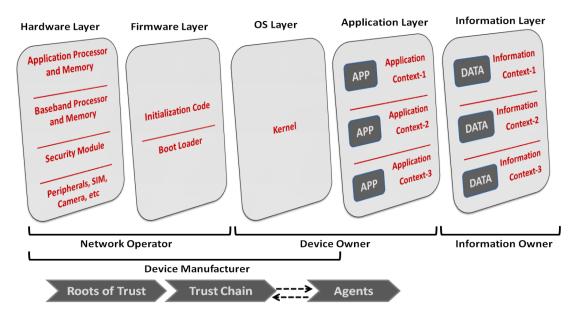

#### 2.2.3 Mobile Device Security Architecture:

Similar to other computing devices, mobile device architecture comprises of a stack of hardware, software and firmware. The higher level of the stacks depend on the lower levels for various services and interfaces and consider them as trustworthy as they have limited access of those levels. Figure 2.1 describes the architecture of mobile devices. [3]

#### 1. Hardware Layer:

This is the lower most layer of the architecture and includes the hardware components of the device. These components are either deployed by the chipset or device manufacturer of the mobile device. The security components operating at this level are vital and serve as the foundation of trust for higher levels of the stack.

Figure 2.1: NIST's Mobile Device Architecture

#### 2. Firmware Layer:

Firmware is a secure set of code that communicates with the mobile device hardware. Firmware is typically written by the device manufacturer. It includes the secure boot code that initializes the firmware and the hardware components and boots the OS. This layer may also contain some of the ROTs supporting the hardware ROT's to provide the security capabilities.

#### 3. OS Layer:

The OS Layer includes the OS kernel, PEE, and system service components along with their configuration data. The operating system is typically approved by the device manufacturer and controlled by the Device Owner. The components of this layer create a secure environment to establish a secure communication between the interfaces and device hardware and to implement security policies. The OS kernel offers application isolation, in collaboration with device integrity and protected storage incorporated in hardware and firmware of the device.

#### 4. Application Layer:

Application Context is responsible for executing the applications. The OS kernel responsible for providing application isolation prevents applications from accessing other

applications container and modifying their user data, configuration data or code. This application isolation capability allows the devices to execute trusted and un-trusted applications simultaneously while at the same time providing the application isolation assurance to the users.

#### 5. Information Layer:

Each Information Context is managed and controlled by its own information owner. Information owners configure their own security requirements and policies of accessing, processing and storing their data on the device. Information owners should not have access permission to modify or temper OS or applications components without the permission of device owner. But information owners should be assured of the secure functionality of the device and that the device platform's security capabilities always run in a trustworthy state while access to information owner's data is managed by their own configured policies.

#### **2.3 TPM MOBILE Specifications**

With the increased utilization of diverse connected devices mainly mobile phones and tablets, have fundamentally transformed our life styles where we now can access personal networks, bank accounts and business documents wherever and whenever required. To take full benefit of the richness and connectivity of these devices, there is a need to control the associated risks. This need activated to emerge two key platform security technologies; Global Platform's Trusted Execution; Environment (TEE) and Trusted Computing Group's (TCG) Mobile Trusted Module (MTM). These two technologies work together in a unified manner called TPM MOBILE to provide security and improved services to its consumers.

#### 2.3.1 TPM Specifications:

TPM is an international standard for a secure crypto-processor, which is a dedicated hardware designed for secure processing in the devices. Since 2006 laptops and desktops are manufactured with the in build TPM chips. TCG in 2003 developed the first version of standard of TPM known as TPMv.1.2. Some of its salient features include strong cryptographic algorithms for hashing, authentication and authorization prevalent at

time of standardization such as SHA-1, RNG, RSA and HMAC. Moreover a single storage hierarchy model was presented to store data, keys and different mobile platforms. Later as the time passed, some of the specifications became obsolete and a need arose to modify the standard. Hence in 2012, TPM 2.0 was published which addressed many of the same use cases of TPM v1.2 and provided many same features with enhanced security capabilities to provide a high level of security assurance for desktop and laptops. TPM 2.0 is not backward compatible to TPM v1.2. TPM v2.0 provides stronger cryptographic algorithms than TPM v1.2 and also discarded the obsolete algorithms which were supported previously. Moreover it provides a three level hierarchy model for platform, storage and endorsement. TPM 2.0 in contrast to TPM v1.2 provides several documents as the reference implementation describing the behavior of codebase thereby ensuring a uniform behavior. The Table 2.1 shows the major differences in specifications of both the policies. Now TPM 2.0 is considered as the internal and accepted standard for hardware security in devices. [25]

| Specification              | <b>TPM v1.2/MTM</b>                          | TPM v2.0                                      |

|----------------------------|----------------------------------------------|-----------------------------------------------|

| Algorithms                 | DES, RSA, SHA-1                              | AES, RSA, P256, SHA-1, SHA-<br>256            |

| Cryptographic<br>Primitive | RNG, SHA-1                                   | RNG, SHA-1, SHA-256                           |

| Hierarchy                  | One (Storage)                                | Three (Storage, Platform,<br>Endorsement)     |

| Root Keys                  | One                                          | Various keys and Algorithms per hierarchy     |

| Authorization              | HMAC, PCR,<br>locality, physical<br>presence | HMAC, Password, Policy                        |

| NV RAM                     | Only Unstructured data                       | Unstructured Data, Counter,<br>Bitmap, Extend |

Table 2.1: Major difference in Specifications of TPM v1.2 and TPM v2.0

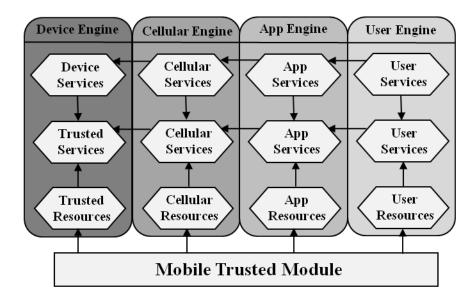

#### 2.3.2 Mobile Trusted Module (MTM):

MTM is security architecture with its origin lying in the TPM v1.2 and approved by TCG for use in mobile devices. It is anticipated to provide the same security and protocol interoperability as desktops and laptops, but with some enhancements for mobile devices... In 2008 TCG gave the specifications for MTM which were derived from TPM v1.2 with some changes for the mobile platform. The main changes introduced in the MTM that make it dissimilar from the TPM v 1.2 specifications are: [27,28]

- The idea of secure boot is initiated. This means that the boot sequence is not only calculated, but also stopped when tempered software is detected. This enhances the integrity of mobile systems and is an important building block for security services or for those which focus on regulatory approvals.

- 2) The TCG mobile specification allows the MTM to be explicitly implemented not only in hardware but also in alternative implementations such as software or firmware. The MTM is considered as a functionality which makes it possible for device manufacturers to implement it as a privilege to their existing architectures.

- It supports to run several parallel MTM instances of multiple stakeholders on the same device while still fulfilling the TCG specifications.

Figure 2.2: Generic Architecture of MTM

The MTM specifications are dynamic and scalable allowing multiple MTMs called engines interlocked with each other and under the control of different stakeholders. Stakeholders include device manufacturers, mobile network operators, application providers and the users; as shown in figure 2.2. Ideally in a mobile platform a single MTM hardware should be accessed by different engines with each engine as a notion of its own trusted services. Each mobile platform engine should support:

- 1) Functionality to implement trusted and non-trusted services related to different stakeholders.

- 2) Self-test to find out the trustworthiness of its own state.

- Secure storage of cryptographic keys; such as endorsement key, attestation identification keys and migration key.

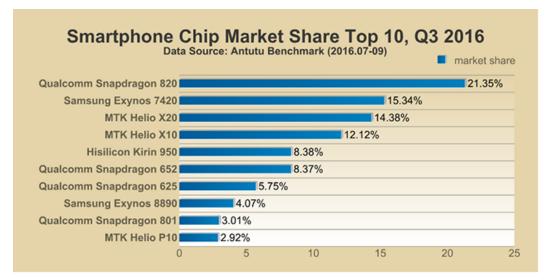

#### 2.3.3 The GlobalPlatform TEE:

The GlobalPlatform TEE categorizes a consistent isolation environment for SoC's for executing sensitive data, code and resources separately from the main OS environment. This isolation is possible due to the hardware architecture and the boot process utilizes hardware ROTs embedded in the SoC to make it robust against software and different probing attacks. Moreover prior to execution the applications running in the TEE are cryptographically verified, leading to high integrity assurance. Also it can be used as a distinct security coprocessor. It provides a trusted 'bridge' between the user and other security technologies such as Secure Element access control on one side and secured user interface on the other side.

The functionality of the Trusted Applications is used by the main OS and applications via a standardized 'Client API' which run normally in their own environment. Trusted Applications are implemented in the Internal API which provides assurance of secure access to resources, different cryptographic algorithms and storage regardless of the underlying SoC hardware.

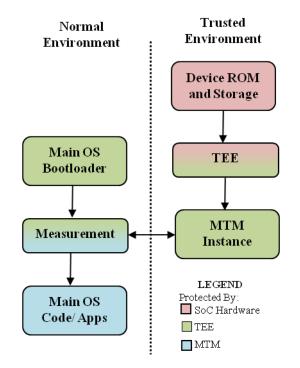

### 2.4 TPM MOBILE Security Model

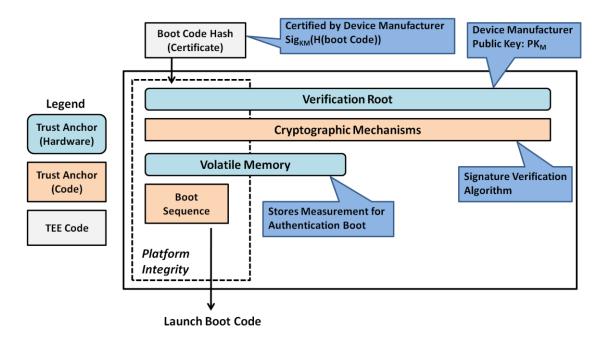

TPM Mobile security model unifies the hardware security architecture proposed by the MTM model and GlobalPlatform TEE. The security of the TPM MOBILE starts with the boot process. The hardware ROT which mainly is an integrity key embedded on the processor starts its boot security. During the later stages of the boot, applications are verified cryptographically to make sure that authorized software is running on the device as shown in the figure 2.3

Figure 2.3: TPM MOBILE Boot Process

After the secure boot the main OS can be accessed at any time which runs in a secure environment of the TEE, protected by the strong hardware mechanisms from the calling process. Hence the device security is ensured at all times during the boot chain process and the secure boot process of the TEE completes before handing over to the TPM MOBILE instance to provide protected boot services to the main OS. Therefore, the TEE provides the mandatory security bridge between the TCG-based main OS security model and the device's base security mechanisms simultaneously with minimal changes in the software design.

The security model as illustrated above works due to the chain of trust from one component to the next is ensured and cryptographically protected. While the specific implementation details differ, they must comply with the TEE specification and TPM-MOBILE deployed running on them, ensuring trustworthy protection and portability

across mobile devices. Figure 2.4 shows the protection hierarchy trust chain for the TPM MOBILE data and operation.

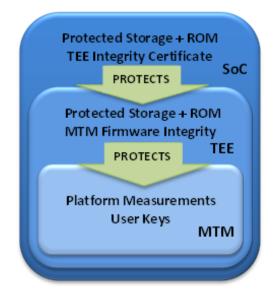

**Figure2.4: Mobile Device Protection Hierarchy**

Hence the three hardware security capabilities illustrated by NIST are achieved as follows:

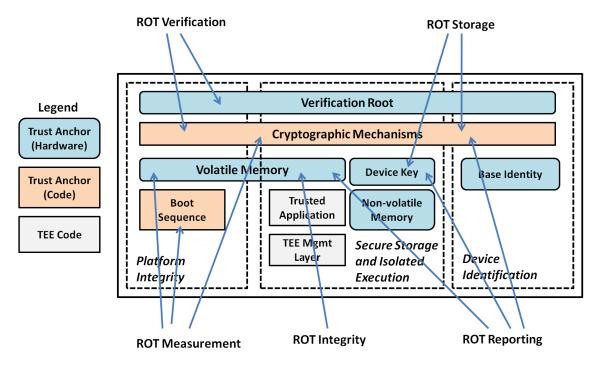

Figure 2.5: Platform Integrity in TPM Mobile Security Model

#### 1) Platform Integrity:

This will be achieved through the mechanism of secure boot. The device will run a secure boot code present in the hardware using root and device manufacturer keys and will calculate the boot hash using stored and trusted cryptographic algorithms. This calculated has will be checked with the hash certificated stored by the device and verified. If verification passes the system will boot otherwise in case of failure the system will stopped. Figure 2.5 shows the phenomenon.

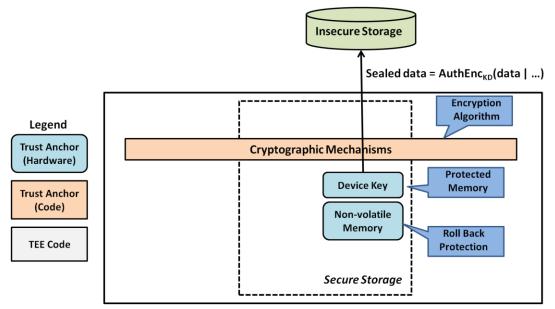

#### 2) Secure Storage:

This is achieved by having the trusted hardware its dedicated volatile and nonvolatile memory which can be isolated from the insecure memory portion. Moreover no confidential data is sent in plain text to the insecure memory and is encrypted using the device key and cipher text is stored on the insecure memory. The figure 2.6 shows the phenomenon.

Figure 2.6: Secure Storage in TPM Mobile Security Model

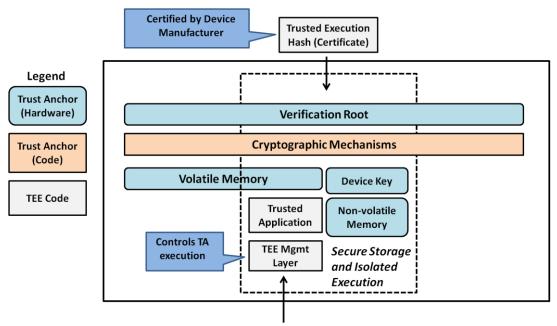

#### 3) Isolated Execution:

Trusted application run within the trusted hardware location. All the client applications before launch are authenticated using the application's public key. Afterwards an isolated and dedicated memory is allocated to the application to execute and to prevent data exchange among different applications. Moreover whenever secure services are requested by the applications they are executed in the secure hardware location. The figure 2.7 illustrates the isolated execution components involved.

**TEE Entry From Rich Execution Environment**

Figure 2.7: Isolation Execution in TPM Mobile Security Model

The figure 2.8 represents the components involved in the five hardware roots of trust specified by the NIST in order to develop a secure hardware system while implementing the security capabilities;

## 2.5 Analysis of Standards

In the above section we have analysis two sets of standards; one is the NIST hardware rooted standard and other is the TCG's TPM Mobile standard.

#### 2.5.1 Comparative Analysis of Standards:

The major difference between the above mentioned two sets of standards is that NIST provides the key components and capabilities required for the manufactures to develop a secure mobile device whereas TPM Mobile also describes how these key components can be used to develop a secure device. Moreover it also gives the TEE architecture to use these hardware rooted security components on the upper layer in a trustworthy manner. NIST has introduced a new hardware root of trust named ROT for integrity for integrity checking of the measurements and processes taking place in the device.

Figure 2.8: Mapping of ROT's For Security Capabilities

While analyzing the standards provided by TCG, TPM 2.0 is the internationally accepted and implemented security standard. TPM 2.0 is the enhanced security standard of TPM v1.2 but it is not backward compatible to it. The major differences in both the standards are illustrated in table 2.1. Furthermore TCG developed the standard for mobile devices called MTM which was derived from TPM v1.2. It used the specifications provided in TPM version with some changes for the mobile environment which included the multi-stack holder environment and allowing to run multiple MTM instances on the same device. The concept of secure boot was introduced. Moreover the compulsion to implement TPM security components in hardware was removed. Developers have been provided flexibility to implement these security features in hardware, software or firmware upon their own requirements and design. The question of how to provide theses security facilities to the OS and application layer was resolved by Global Platform TEE which provided the specifications and secure boot chain mechanism of TEE to develop a

secure trusted environment for the mobile devices. Together the MTM and TEE provide a complete security standard TPM MOBILE for the mobile devices.

#### 2.5.2 Analysis of MTM Specifications:

In computing systems mutual trust among peer systems is established through attestation process for integrity assurance. Secure attestation is ensured by cryptographically protected hardware that is resistant to software attacks. TCG published the improvement in specifications for trusted computing on mobile devices and TPM is considered to be the root of trust and enables secure attestation by providing secure cryptographic primitives for signatures and hashes. However, the similarities of MTM and TPM have raised many implementation concerns and respective challenges. The following are some of the salient observations.

- 1) MTM provides relatively weak security policies of the time as it is derived from TPM v1.2. TPM v2.0 promises enhanced security policies and have proven to be a better standard in high computing devices such as desktops and laptops. For example, MTM specifies DES and SHA1 as encryption and hashing algorithms whereas they are now obsolete and better security algorithms such as AES, SHA256, etc are present and added as a standard in the later version TPM 2.0. Moreover, MTM mandates single storage hierarchy model which is unsuitable for the mobile environment having multiple stalk holder hierarchy. Hence a modified version of MTM should be presented which must be comparable to TPM v2.0 providing enhanced and up to date features and specifications.

- 2) TCG enlightens the functionality aspects of MTM while not focusing on the implementation technique required in developing such modules. This aspect has been left over for the manufactures to define their implementations strategies by themselves which does not makes one manufacture's model compatible with the other one. Moreover these solutions are closed form solutions. Hence there is a need to modify the standard to incorporate the reference implementation techniques and to bring all the manufacturers on a unified platform.

- 3) TCG specifies a separate deployment of TPM functionality in an isolated module which may be unable to yield the desired trade-off between cost, security and

performance. Mobile devices are now providing more computing resources and performance but have a serious constraint of device size and power management. High security requires high computing resources and physical area utilizing more power resources and hence making the device more costly. On the other hand software implementation of MTM will not be able to meet the security challenges. Therefore there is a need to standardize a suitable implementation technique for the mobile device environment and to yield the desired trade-off between cost, power, security and performance.

- 4) The algorithms defined for security in MTM support cryptographic algorithms which require large computation power and resources, and hence are less suitable choices for low computing resource constraint processors. e.g. SHA-1 as a hashing algorithm and RSA as a public key algorithm require more computing resources and high power consumption. Suitable algorithms with less computing resources should be suggested for the mobile computing environments.

- 5) The implementation technique of the cryptographic algorithms does not specify cryptographic mode of operation. A specific cryptographic mode of operation that is resilient to channel errors should be suggested in the policy for the implementation purposes.

- 6) The last concern is related to the robust implementation of cryptographic primitives. Typically, cryptographic co-processors occupy large silicon area and have poor flexibility. On the contrary, a co-design approach of hardware and software allows algorithm flexibility to be achieved at relatively less hardware cost and smaller surface area.

The modified standard should mitigate the limitations of TCG specifications discussed above while providing a new concept for the implementation of the MTM security services. Suggestions for the modified version will be discussed in the last chapter where the solution implementation technique for the mobile devices will be proposed.

# 2.6 Selection of Cryptographic Algorithms

The selection of cryptographic algorithms for the security of embedded systems is a critical and vital element in strengthening their secure architecture. Both TPM v2.0 and MTM have provided conventional cryptographic algorithms for the purpose of encryption decryption, hashing, digital signatures etc. For example TPM v2.0 proposes AES for symmetric ciphering and deciphering, RSA for asymmetric ciphering and deciphering and SHA-256 for hashing functionality. The proposed cryptographic algorithms are popular for their cryptographic strength and also standardized by NIST and NSA as one of the best secure crypto algorithms. But these algorithms are suitable for devices embedded with high power processors meant for excessive computing such as laptops, desktops, tablets and smart phones. On the contrary these algorithms fail to meet the power, processing and memory constraint environment of various wearable and IoTs which include Bluetooth, NFC, RFID and smart card systems. Therefore a new branch of cryptography was introduced named as lightweight cryptography. Lightweight ciphers were developed for such resource constraint devices providing the same comparable security as conventional crypto algorithms but utilize less power and memory due to smaller key size, smaller block size, less number of rounds and relatively simpler design architecture.

## 2.6.1 Lightweight Block Ciphers:

Some of the lightweight block algorithms implemented widely and known for their high strength and throughput are listed below in table 2.2 along with their features. [11,13,14]

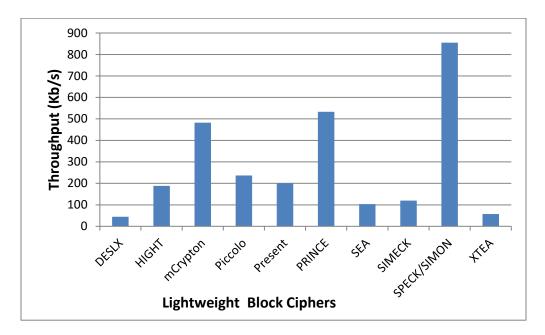

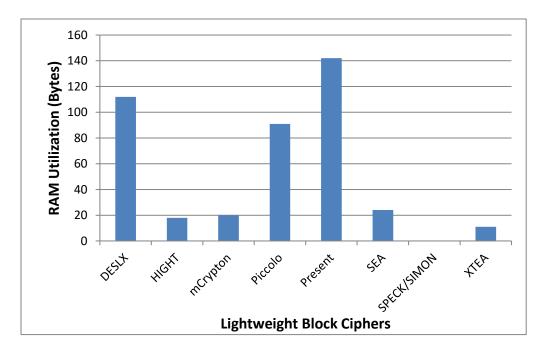

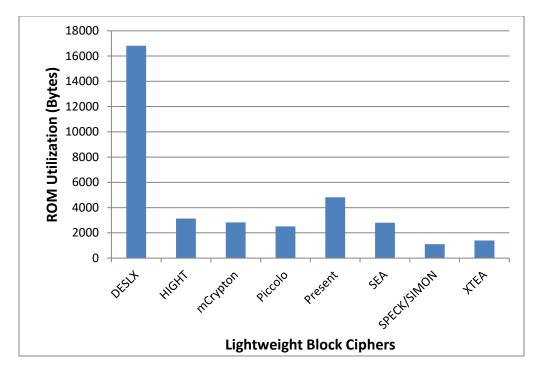

The cipher with the maximum throughput and minimum memory usage is considered to be the better cipher. From the above listed ciphers the best cipher having the maximum through put is Simon/Speck with 855 Kb/s of throughput. After that PRINCE and mCrypton seem to provide a better through put of 533 Kb/s and 482 Kb/s respectively. Figure 2.9 demonstrates their relative through put graph. Figure 2.10 and 2.11 illustrates the graphs of memory usage on RAM and RAM. It depends on the design criterion of the developer that whether it uses more ROM space for the algorithm code and states storage or provides an appreciable amount of RAM for processing. From the

algorithms listed DESLX uses the maximum of ROM space but Present utilizes maximum of RAM Space. Observing both the metrics simultaneously, Speck/Simon uses minimum of Ram space and no RAM is util36ed during processing. It stores its intermediate states and processing data in registers. Hence Speck/Simon provides an integrated solution if maximum throughput and minimum storage utilization.

Table2.2: List of Lightweight Block Cryptographic Algorithms and their Performance Metrics

| S.No. | Lightweight<br>Algorithm | Key Size        | Block<br>Size | No. of<br>Rounds | Throughput<br>(Kb/s @<br>100kHz) | Power<br>Consumed<br>(µW)/bit | Memory<br>Utilized<br>(bytes) |                      |

|-------|--------------------------|-----------------|---------------|------------------|----------------------------------|-------------------------------|-------------------------------|----------------------|

|       |                          |                 |               |                  |                                  | (μ • • • )/ υπ                | RAM                           | ROM                  |

| 1     | DESLX                    | 184             | 64            | 16               | 44.4                             | 1.6                           | 112                           | 16816                |

| 2     | HIGHT                    | 128             | 64            | 32               | 188.2                            | -                             | 18                            | 3130                 |

| 3     | mCrypton                 | 64<br>96<br>128 | 64            | 12               | 482.3                            | -                             | 18<br>20<br>24                | 2726<br>2834<br>3108 |

| 4     | Piccolo                  | 80              | 64            | 25               | 237.04                           | 4.42                          | 79                            | 2434                 |

|       |                          | 128             |               | 31               | 193.9                            | 2.78                          | 91                            | 2510                 |

| 5     | Present                  | 80              | 64            | 31               |                                  | 2.78                          | 142                           | 4814                 |

|       |                          | 128             |               |                  | 200                              | 3.67                          | 142                           | 4964                 |

| 6     | PRINCE                   | 128             | 64            | 12               | 533.3                            | 5.8                           |                               |                      |

| 7     | SEA                      | 96              | 96            | 93               | 103                              | 3.218                         | 24                            | 2804                 |

| 8     | SIMECK                   | 64              | 32            | 32               | 88.9                             | 0.606                         | -                             | -                    |

|       |                          | 96              | 48            | 36               | 120                              | 0.875                         |                               |                      |

|       |                          | 128             | 64            | 44               | 133.3                            | 1.162                         |                               |                      |

| 9     | SPECK/                   | 64              | 32            | 32               |                                  | 3.98                          | 0                             | 324                  |

|       | SIMON                    | 72/96           | 48            | 36               | 855                              | 3.32                          | 0                             | 556                  |

|       |                          | 96/128          | 64            | 42/44            |                                  | 3.65                          | 0                             | 602                  |

|       |                          | 128/192/256     | 128           | 68/69/72         |                                  | 4.20                          | 0                             | 1108                 |

| 10    | XTEA                     | 128             | 64            | 64               | 57.1                             | 19.5                          | 11                            | 1394                 |

Figure 2.9: Comparative Analysis of Throughput of Popular Lightweight Block Cipher

Figure 2.10: Comparative Analysis of RAM Utilization of Popular Lightweight Block Cipher

Figure 2.11: Comparative Analysis of ROM Utilization of Popular Lightweight Block Cipher

Out of the above listed light weight ciphers NIST has recommended DESL, SEA, TEA, SIMON and SPECK. Piccolo algorithm provides the best results of throughput and relative hardware size and is prioritized when implementing the algorithms in hardware. Simon and Speck are the algorithms made by NSA but have not publically released them. SPECK targeted for hardware and SIMON targeted for software implementation have proven to be among the best algorithms for resource constraint devices.

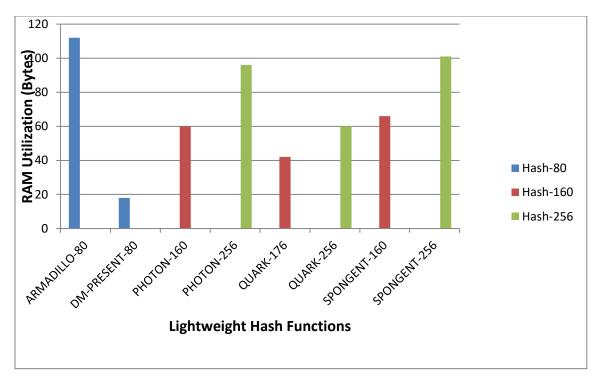

### 2.6.2 Lightweight Hash Functions:

Table 2.3 shows the list of lightweight hash functions implemented widely along with their performance metrics [15,16]. QUARK, PHOTON, DM-PRESENT and SPONGENT are the hashing functions standardized by NIST. As shown from figure 2.12 among the listed lightweight hashing functions QUARK seems to fulfill the tradeoff of high throughput, less power consumption and minimum memory usage. Whereas PHOTON and SPONGENT provide a wide range of digest size options for implementation. The analysis carried out related to the lightweight algorithms will be used in the last chapter were the suggested solution will be presented.

| S.No | Lightweight<br>Algorithm | Digest<br>Size | Rate | Internal<br>State<br>Size | Throughput<br>(Kb/s @<br>100kHz) | Power<br>Consumed<br>(µW)/bit | Memory<br>Utilized<br>(bytes) |       |

|------|--------------------------|----------------|------|---------------------------|----------------------------------|-------------------------------|-------------------------------|-------|

|      |                          |                |      | 5                         |                                  | (μ • • • )/ υπ                | RAM                           | ROM   |

| 1    | ARMADILLO                | 80             | 48   | 256                       | 109                              | 44                            | 112                           | 16816 |

|      |                          | 128            | 64   | 384                       | 1000                             | -                             | -                             | -     |

|      |                          | 160            | 80   | 480                       | 100                              | -                             | -                             | -     |

|      |                          | 192            | 96   | 576                       | 100                              | -                             | -                             | -     |

|      |                          | 256            | 128  | 768                       | 100                              | -                             | -                             | -     |

| 2    | DM-                      | 64             | 80   | 64                        | 242.42                           | 6.28                          | 18                            | 3130  |

|      | PRESENT                  | 64             | 128  | 64                        | 387.88                           | 7.49                          |                               |       |

| 3    | Lesamnta-LW              | 256            | 128  | 256                       | 125.55                           | -                             | -                             | -     |

| 4    | PHOTON                   | 80             | 16   | 100                       | 2.82                             | 1.59                          |                               |       |

|      |                          | 128            | 16   | 144                       | 1.61                             | 2.29                          |                               |       |

|      |                          | 160            | 36   | 196                       | 2.70                             | 2.74                          | 60                            | 598   |

|      |                          | 224            | 32   | 256                       | 1.86                             | 4.01                          |                               |       |

|      |                          | 256            | 32   | 288                       | 3.21                             | 4.55                          | 96                            | 364   |

| 5    | QUARK                    | 136            | 8    | 136                       | 1.47                             | 2.44                          |                               |       |

|      |                          | 176            | 16   | 176                       | 2.27                             | 3.10                          | 42                            | 974   |

|      |                          | 256            | 32   | 256                       | 3.13                             | 4.35                          | 60                            | 1106  |

| 6    | GLUON                    | 128            | 8    | 136                       | 12.12                            | -                             | -                             | -     |

|      |                          | 160            | 16   | 176                       | 32                               | -                             | -                             | -     |

|      |                          | 224            | 32   | 256                       | 58.18                            | -                             | -                             | -     |

| 7    | SPONGENT                 | 80             | 8    | 88                        | 0.81                             | 1.57                          | -                             | -     |

|      |                          | 128            | 8    | 136                       | 0.34                             | 2.20                          | -                             | -     |

|      |                          | 160            | 16   | 176                       | 0.40                             | 2.85                          | 66                            | 598   |

|      |                          | 224            | 16   | 240                       | 0.22                             | 3.74                          | -                             | -     |

|      |                          | 256            | 16   | 272                       | 0.17                             | 4.21                          | 101                           | 364   |

Table2.3: List of Lightweight Hashing Functions and their Performance Metric

Figure 2.12: Comparative Analysis of RAM Utilization of lightweight Hash Functions

## 2.7 Conclusion

In this chapter we have highlighted various hardware rooted mobile security standards available for the mobile manufacturers to develop secure mobile systems. The relative comparison has also been carried out and it can be concluded that NIST lists down the components and capabilities required in developing a secure mobile system whereas TPM Mobile also provides the TEE architecture to use these hardware rooted components efficiently on the upper layers of the mobile device architecture. Analysis of all these standards and their comparison was carried out. Moreover some of the shortcomings analyzed in MTM standard were also discussed. At the end of the chapter concept of lightweight cryptography was introduced and different lightweight block ciphers and hashing algorithms are listed. There relative comparison with respect to throughput, power consumption and memory (RAM and ROM) was carried out. The next chapter will focus on the TPM implementation techniques and the commercial security solutions available in the market.

# MOBILE SECURITY IMPLEMENTATION SOLUTIONS AND THEIR ANALYSIS

# 3.1 Introduction

In the last chapter we highlighted the hardware rooted security standards present for the mobile devices. Also we analyzed these standards and after their comparison listed some of the shortcomings present in the MTM specification. In this chapter we would discuss the key components of a TPM and its implementation techniques for mobile devices. Afterwards we will discuss the different security solutions developed by the industry and will analyze them for the extent to which they comply with the standards. As most of the solutions are dependent on the underlying ARM TrustZone technology, hence an in depth analysis will be carried out of ARM TrustZone. Moreover its shortcomings will also be highlighted.

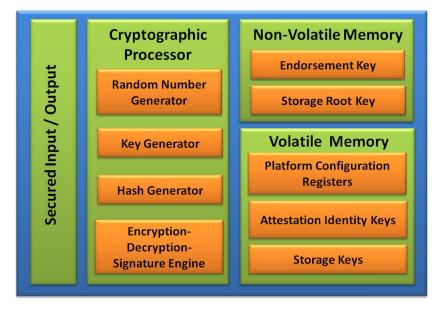

# **3.2** Internal Components of a TPM

TPM is the basic component in the trusted computing devices which offers a hardware root of trust to ensure OS and applications integrity. The TPM is basically a hardware chip embedded with the basic necessary security features like generation of random numbers, cryptographic operations execution, secure storage of vital data and secret keys; as shown in the figure 3.1. TCG gave the specifications compulsory for the TPM in its version 1.2 as the first standard in 2003 followed by its enhanced security version 2.0 in 2008 which is now internationally accepted and implemented in static computing devices. TPM comprises of the following trusted components embedded into a single SoC. [23,24]

## **3.2.1 Secured Input and Output:**

The data transfer on the communication bus takes place after encoding or decoding according to the protocol specified by the programmer. TCG has not specified