# Architecture and Digital Design of a flexible Correlation filter Processor

Author Abdullah Aman Khan 2011-NUST-MS PhD-ComE-02 Supervisor Dr. Saad Rehman

DEPARTMENT OF COMPUTER ENGINEERING COLLEGE OF ELECTRICAL & MECHANICAL ENGINEERING NATIONAL UNIVERSITY OF SCIENCES AND TECHNOLOGY ISLAMABAD MAY, 2014

# Architecture and Digital Design of a flexible Correlation filter Processor

Author

Abdullah Aman Khan 2011-NUST-MS PhD-ComE-02

A thesis submitted in partial fulfillment of the requirements for the degree of MS Computer Engineering

Thesis Supervisor: Dr. Saad Rehman

Thesis Supervisor's Signature:

# DEPARTMENT OF COMPUTER ENGINEERING COLLEGE OF ELECTRICAL & MECHANICAL ENGINEERING NATIONAL UNIVERSITY OF SCIENCES AND TECHNOLOGY, ISLAMABAD MAY, 2014

## Declaration

I certify that this research work titled "Architecture and Digital Design of a flexible Correlation filter Processor" is my own work. The work has not been presented elsewhere for assessment. The material that has been used from other sources it has been properly acknowledged / referred.

Signature of Student Abdullah Aman Khan 2011-NUST-MS PhD-ComE-02

## Language Correctness Certificate

This thesis has been read by an English expert and is free of typing, syntax, semantic, grammatical and spelling mistakes. Thesis is also according to the format given by the university.

Signature of Student Abdullah Aman Khan 2011-NUST-MS PhD-ComE-02

> Signature of Supervisor Dr. Saad Rehman

## **Copyright Statement**

- Copyright in text of this thesis rests with the student author. Copies (by any process) either in full, or of extracts, may be made only in accordance with instructions given by the author and lodged in the Library of NUST College of E&ME. Details may be obtained by the Librarian. This page must form part of any such copies made. Further copies (by any process) may not be made without the permission (in writing) of the author.

- The ownership of any intellectual property rights which may be described in this thesis is vested in NUST College of E&ME, subject to any prior agreement to the contrary, and may not be made available for use by third parties without the written permission of the College of E&ME, which will prescribe the terms and conditions of any such agreement.

- Further information on the conditions under which disclosures and exploitation may take place is available from the Library of NUST College of E&ME, Rawalpindi.

#### Acknowledgements

Foremost, I would like to express my sincere gratitude to my advisor Dr. Saad Rahman for the continuous support of my Masters Study and research, for his patience, motivation, enthusiasm, and immense knowledge. His guidance helped me in all the time of research and writing of this thesis. I could not have imagined having a better advisor and mentor for my Masters study.

Besides my advisor, I would like to thank the rest of my thesis committee Brig. Dr. Shoab A Khan, Dr. Umer Munir, Dr. Usman Akram and Mr. Sajid Gul for their encouragement, insightful comments, and hard questions.

Last but not the least; I would like to thank my family supporting me spiritually throughout my life.

#### Abstract

Dedicated design for pattern recognition techniques can provide processing at higher speed, .Many Real time digital designs provide single functionality, but where speed, scalability and flexibility is required more extensive research is demanded. These special purpose and Application specific designs can provide real time procession for many applications. In this thesis the challenges, problems and design for a correlation patteren recognition processor is presented, The design is based on fixed point representation of binry numbers, further the fixed point representation is used to represent complex numbers as correlation filters are designed in frequency domain. The presented design is an educational purposes design, which provides mechanism to handle matrices on chip and also is capable of performing simple matrices operation like arithmetic and matrix handling. The matrices are represented with simple identifiers and using application specific micro instruction provided in the design assist in processing of many complex operations which are useful for solving bigger problems when summed up to gather in a meaning full manner. The design was successfully implemented and tested using VHDL language using Xilinx tool. The objective of this work was to get an area & time efficient architecture that can be used as a standalone processor with built in all resources necessary for an embedded pattern recognition application.

### **Table of Contents**

| Acknowledgements            | ii  |

|-----------------------------|-----|

| Abstract                    | iii |

| List of Tables              | ix  |

| List of Figures             | X   |

| Chapter 1 Introduction      | 13  |

| 1.1 Typical Methods:        | 16  |

| 1.2 Motivation              | 18  |

| 1.3 Challenges              | 21  |

| 1.3.1 Flexibility           | 21  |

| 1.3.2 Cost Effectiveness    | 21  |

| 1.3.3 Common Requirements   | 21  |

| 1.4 Orientation of Thesis   | 23  |

| Chapter 2 Literature Review | 24  |

| 2.1 Correlation Filters     | 24  |

| 2.1.1 MACH Filter           | 24  |

| 2.1.2 EMACH Filter          | 26  |

| 2.2 The Fourier Transform   | 28  |

| 2.3 Fourier Transform Matrix Representation      |    |

|--------------------------------------------------|----|

| 2.4 Fixed Point Representation of Binary Numbers |    |

| Chapter 3 Implementation                         |    |

| 3.1 Main Memory                                  | 33 |

| 3.2 Memory Manager                               |    |

| 3.3 Sub to Index                                 |    |

| 3.4 Sequence Guide                               | 41 |

| 3.5 Arithmetic and Logic Unit                    | 43 |

| 3.6 Control Unit                                 | 44 |

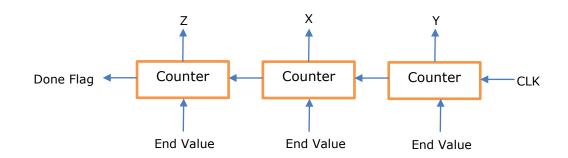

| 3.7 Counter and Counter banks                    | 45 |

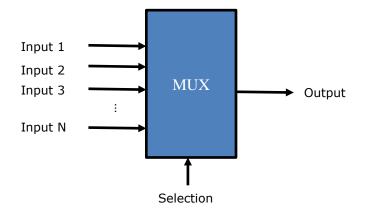

| 3.8 Multiplexer                                  | 48 |

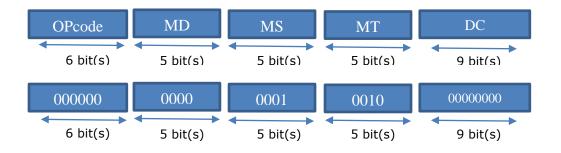

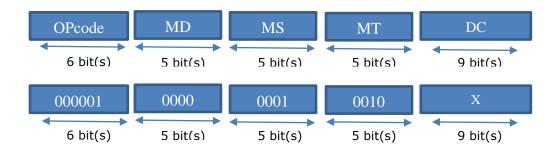

| Chapter 4 Instruction Set Architecture           | 50 |

| Matrix Multiplication with Matrix                | 50 |

| Matrix dot multiplication with Matrix            | 50 |

| Matrix dot multiplication with immediate Value   | 51 |

| Matrix dot multiplication with stored Value      | 51 |

| Matrix dot division with Matrix                  |    |

| Matrix dot Division with stored Value            |    |

| Matrix dot Division with Immediate Value         | 52 |

| Matrix Addition with Matrix                   | . 53 |

|-----------------------------------------------|------|

| Matrix Subtraction with Matrix                | 53   |

| Matrix Addition with stored Value             | 54   |

| Matrix Subtraction with stored Value          | . 54 |

| Matrix dot Power with stored Value            | . 55 |

| Matrix Subtraction with immediate Value       | 55   |

| Matrix Addition with immediate Value          | 55   |

| Matrix Raised to the Power of immediate Value | . 56 |

| Transpose of Matrix                           | 56   |

| Set Conjugate Flag                            | . 57 |

| Re-Set Conjugate Flag                         | . 57 |

| Fourier Transform First Pass                  | . 58 |

| Fourier Transform Second Pass                 | . 58 |

| Scalar Multiplication                         | . 58 |

| Scalar Addition                               | . 59 |

| Scalar Subtraction                            | 59   |

| Scalar Division                               | . 59 |

| Scalar Power                                  | . 60 |

| Scalar Addition with immediate Value          | . 60 |

| Scalar subtraction with immediate Value         |

|-------------------------------------------------|

| Scalar Division with immediate Value            |

| Scalar Power with immediate Value               |

| Jump if equal 62                                |

| Jump if not equal 62                            |

| Jump if is less than or equal                   |

| Jump if is Greater than or equal                |

| Unconditional Jump 64                           |

| Jump if is less than                            |

| Jump if is Greater than                         |

| Copy real part of matrix                        |

| Loading a value to a memory Location            |

| Loading negative a value to a memory Location   |

| Copy a memory location to a new location        |

| Copy a Matrix location to a new Matrix location |

| Copy a Column of a matrix                       |

| Load Memory content to special register         |

| Write from special register                     |

| Load row and column Address                     |

| Write to special        | l register (row and column)         | 68 |

|-------------------------|-------------------------------------|----|

| Save from Spec          | ial Register                        | 69 |

| Initialize a new        | matrix                              | 69 |

| Reshape Matrix          | ۲                                   | 69 |

| Chapter 5 Data paths an | nd Design                           | 71 |

| 5.1 Requirement         | nt Details                          | 71 |

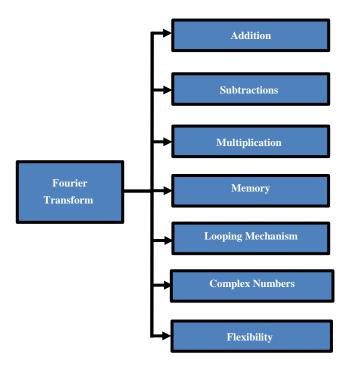

| 5.2 Fourier             | Transform                           | 71 |

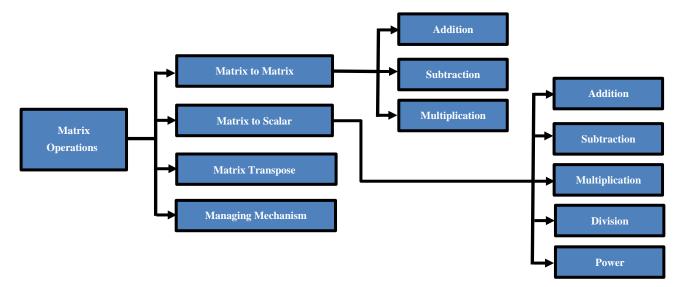

| 5.3 Basic M             | latrix Operations                   | 72 |

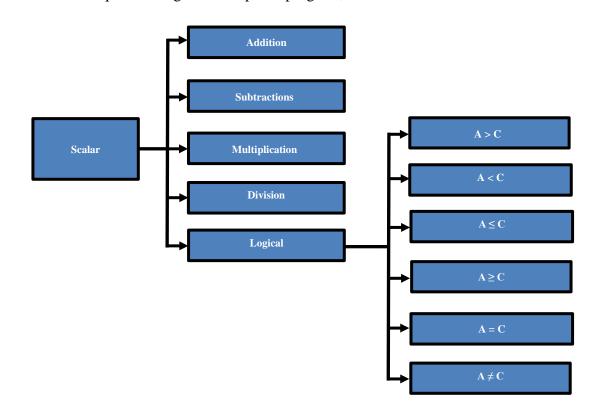

| 5.4 Scalar A            | Arithmetic                          | 73 |

| 5.5 Fourier Tra         | nsform Design                       | 74 |

| 5.6 Representat         | ion of a complex Number             | 79 |

| 5.7 Data Paths f        | for Individual instruction Types    | 80 |

| 5.8 The Program         | n Counter                           | 80 |

| 5.9 On chip Me          | emory Manager                       | 81 |

| 5.10 Sub-Index          | to single index Generation          |    |

| 5.11 Counter ar         | nd Program Counter clock Selection: | 84 |

| 5.12 The Matrix         | x Addition/Subtraction data path    |    |

| 5.13 The Matrix         | x Multiplication                    | 86 |

| 5.14 The Matrix         | x Transpose                         | 87 |

| 5.15 The Matrix Operations with a Scalar Value place in memory   | . 88 |

|------------------------------------------------------------------|------|

| 5.16 Matrix Operations with an Immediate Value                   | 89   |

| 5.17 Scalar Operations (In Memory)                               | 90   |

| 5.18 Scalar Operations Immediate                                 | 90   |

| 5.19 Jumps and Branching Instructions                            | 91   |

| 5.20 Variable Clock Cycle Implementation along with single cycle | 92   |

| 5.21 Main Architecture Design                                    | 92   |

| Chapter 6 Simulation Results                                     | 94   |

| Computing DFT                                                    | 94   |

| Matrix Multiplication                                            | 96   |

| Matrix Arithmetic                                                | 98   |

| Matrix Transpose                                                 | 99   |

| Branching                                                        | 101  |

| Scalar Arithmetic                                                | 102  |

| Instruction Memory Contents View                                 | 103  |

| EMACH Filter Calculation results                                 | 104  |

| Chapter 7 Future Work and Conclusion                             | 105  |

| Future Work                                                      | 107  |

| Pipeline                                                         | 107  |

| Embedding  | FFT    |  |

|------------|--------|--|

| System I/O | design |  |

| References |        |  |

List of Tables

| Table 6-1 DFT Results comparison with MATLAB                            | . 97 |

|-------------------------------------------------------------------------|------|

| Table 6-2 Matrix Multiplication Results comparison with MATLAB          | 100  |

| Table 6-3 Matrix Multiplication Addition Results comparison with MATLAB | 101  |

| Table 6-4 Filter Results comparison with MATLAB                         | 106  |

# List of Figures

| Figure 1-1: A fingerprint diagram with some salient features (B. V. K. Vijaya Kumar). 17                    |

|-------------------------------------------------------------------------------------------------------------|

| Figure 1-2: Typical Flow chart for typical Pattern Recognition system                                       |

| Figure 1-3: (a) input pattern (b) Reference image (c) Correlation Plane (correlation results of (a) to (b)) |

| Figure 1-4: A standalone Model for CPR                                                                      |

| 1 igure 1-4. A standarone Woder for CI R                                                                    |

| Figure 1-5: Diagram representing the requirements to perform CPR 25                                         |

| Figure 2-1: A Correlation Filter application flow                                                           |

| Figure 2-2 : Signal represented as a sum of sinusoidal (Kamisetty Rao)                                      |

| Figure 2-3: Word Representation of fixed point binary (Khan)                                                |

| Figure 2-4 : Representation of fixed point numbers (Khan)                                                   |

| Figure 3-1: Elements of two Matrices placed in same memory (a memory overview) 36                           |

| Figure 3-2 : Main memory module layout                                                                      |

| Figure 3-3: Description of common features of clock cycle                                                   |

| Figure 3-4 : Layout of memory manager inputs and outputs                                                    |

| Figure 3-5 : Working Mechanics of Memory Manager                                                            |

| Figure 3-6: Linear storage of matric in memory showing their base addresses 40                              |

| Figure 3-7: (a) Representation of Matrix in Subscript (b) Single index representation (row                  |

| oriented) (c) Single index representation (column oriented)                                                 |

| Figure 3-8: Conversion of Subscript index to Single Index                                                   |

| Figure 3-9: Conversion of Subscript index to Single Index                            | 3 |

|--------------------------------------------------------------------------------------|---|

| Figure 3-10 : Source, Destination and Target Description 4                           | 4 |

| Figure 3-11 : The Operation Guide Contents view (Matrix Arithmetic) 4                | 4 |

| Figure 3-12: The Operation Guide Contents view                                       | 5 |

| Figure 3-13 : Layout of the ALU 4                                                    | 6 |

| Figure 3-14: Control Unit layout 4                                                   | 6 |

| Figure 3-15 : Inside view of the lookup table for Control Panel 4                    | 6 |

| Figure 3-16 : Control Unit layout 4                                                  | 7 |

| Figure 3-17 : Mechanism for generating index values for a matrix                     | 8 |

| Figure 3-18 : Gate Level view of the comparator                                      | 9 |

| Figure 3-19 : Internal view of counter                                               | 9 |

| Figure 3-20 : Mechanism for generating index values for matrix multiplications       | 0 |

| Figure 3-21 : A Multiplexer in-out Description 5                                     | 1 |

| Figure 4-1 : Instruction Vector Bits lay out for Matrix Multiplication with Matrix 5 | 2 |

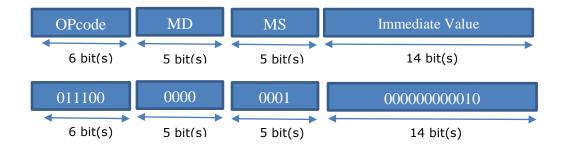

| Figure 4-2 : Bits lay out Matrix dot multiplication with Matrix                      | 3 |

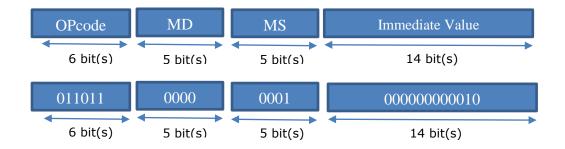

| Figure 4-3 : Bits lay out for Matrix dot multiplication with immediate Value         | 3 |

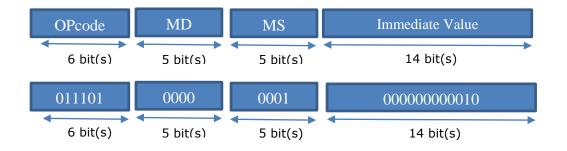

| Figure 4-4 : Bits lay out for Matrix dot multiplication with stored Value            | 4 |

| Figure 4-5 : Bits lay out of Matrix dot division with Matrix                         | 4 |

| Figure 4-6 : Bits lay out for Matrix dot Division with stored Value                  | 4 |

| Figure 4-7 : Bits lay out for Matrix dot Division with Immediate Value   | 55 |

|--------------------------------------------------------------------------|----|

| Figure 4-8 : Bits lay out for Matrix Addition with Matrix                | 55 |

| Figure 4-9 : Bits lay out Matrix Subtraction with Matrix                 | 56 |

| Figure 4-10 : Bits lay out Matrix Addition with stored Value             | 56 |

| Figure 4-11 : Bits lay out of Matrix Subtraction with stored Value       | 56 |

| Figure 4-12 : Bits lay out Matrix dot Power with stored Value            | 57 |

| Figure 4-13 : Bits lay out Matrix Subtraction with immediate Value       | 57 |

| Figure 4-14 : Bits lay out Matrix Addition with immediate Value          | 58 |

| Figure 4-15 : Bits lay out Matrix Raised to the Power of immediate Value | 58 |

| Figure 4-16 : Bits lay out Transpose of Matrix                           | 59 |

| Figure 4-17 : Bits lay out Set Conjugate Flag                            | 59 |

| Figure 4-18 : Bits lay out Re-Set Conjugate Flag                         | 59 |

| Figure 4-19 : Bits lay out Fourier Transform First Pass                  | 60 |

| Figure 4-20 : Bits lay out Fourier Transform Second Pass                 | 60 |

| Figure 4-21 : Bits lay out Scalar Multiplication                         | 61 |

| Figure 4-22 : Bits lay out Scalar Addition                               | 61 |

| Figure 4-23 : Bits lay out Scalar Subtraction                            | 61 |

| Figure 4-24 : Bits lay out Scalar Division                               | 62 |

| Figure 4-25 : Bits lay out Scalar Power                                  | 62 |

| Figure 4-26 : Bits lay out Scalar Addition with immediate Value            | 63 |

|----------------------------------------------------------------------------|----|

| Figure 4-27 : Bits lay out Scalar subtraction with immediate Value         | 63 |

| Figure 4-28 : Bits lay out Scalar Division with immediate Value            | 63 |

| Figure 4-29 : Bits lay out Scalar Power with immediate Value               | 64 |

| Figure 4-30 : Bits lay out Jump if equal                                   | 64 |

| Figure 4-31 : Bits lay out Jump if not equal                               | 65 |

| Figure 4-32 : Bits lay out Jump if is less than or equal                   | 65 |

| Figure 4-33 : Bits lay out Jump if is Greater than or equal                | 65 |

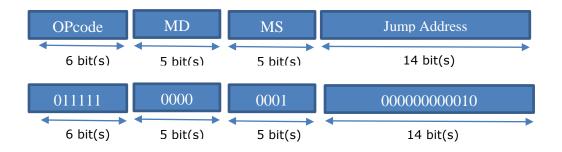

| Figure 4-34 : Bits lay out for Unconditional Jump                          | 66 |

| Figure 4-35 : Bits lay out for Jump if is less than                        | 66 |

| Figure 4-36 : Bits lay out for Jump if is Greater than                     | 67 |

| Figure 4-37 : Bits lay out Copy real part of matrix                        | 67 |

| Figure 4-38 : Bits lay out for loading a value to a memory Location        | 67 |

| Figure 4-39 : Bits lay out Loading negative a value to a memory Location   | 68 |

| Figure 4-40 : Bits lay out Copy a memory location to a new location        | 68 |

| Figure 4-41 : Bits lay out Copy a Matrix location to a new Matrix location | 69 |

| Figure 4-42 : Bits lay out Copy a Column of a matrix                       | 69 |

| Figure 4-43 : Bits lay out Load Memory content to special register         | 69 |

| Figure 4-44 : Bits lay out Write from special register                     | 70 |

| Figure 4-45 : Bits lay out Load row and column Address                              | . 70 |

|-------------------------------------------------------------------------------------|------|

| Figure 4-46 : Bits lay out Write to special register (row and column)               | . 71 |

| Figure 4-47 : Bits lay out Save from Special Register                               | . 71 |

| Figure 4-48 : Bits lay out Initialize a new matrix                                  | . 71 |

| Figure 4-49 : Bits lay out Reshape Matrix                                           | . 72 |

| Figure 5-1 : The sub operations required by Major Operations                        | . 73 |

| Figure 5-2 : Operations required to perform a Fourier transform                     | . 74 |

| Figure 5-3 : Matrix Operations                                                      | . 75 |

| Figure 5-4 : Scalar Operations required                                             | . 75 |

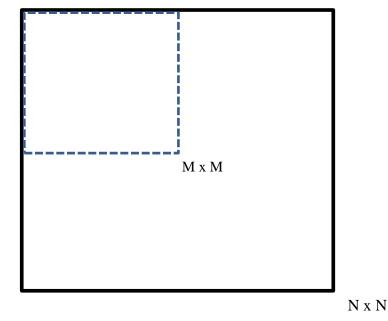

| Figure 5-5 : Truncation of Values from Larger Generic Matrix for computation of DFT | Г79  |

| Figure 5-6 : Representation of a complex Number (Memory Location View)              | . 81 |

| Figure 5-7 : Representation of a complex Number (Memory Location View)              | . 82 |

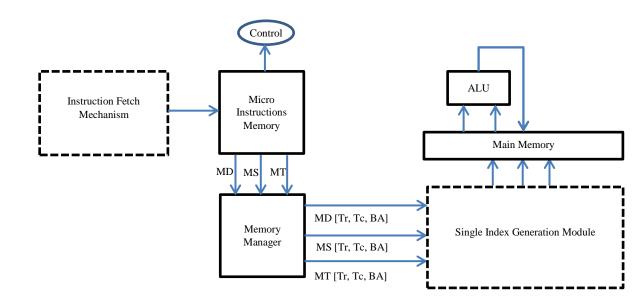

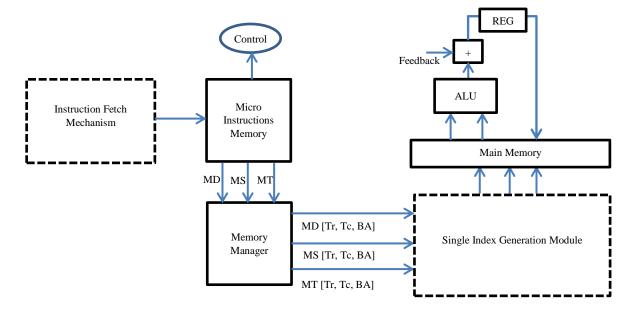

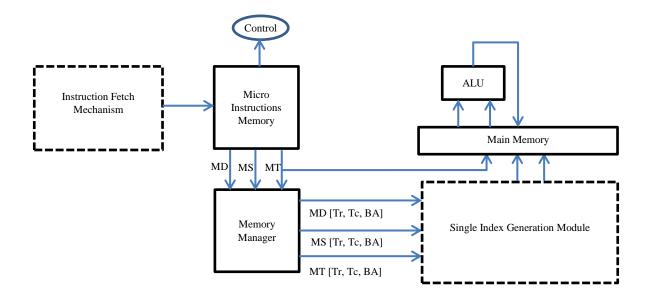

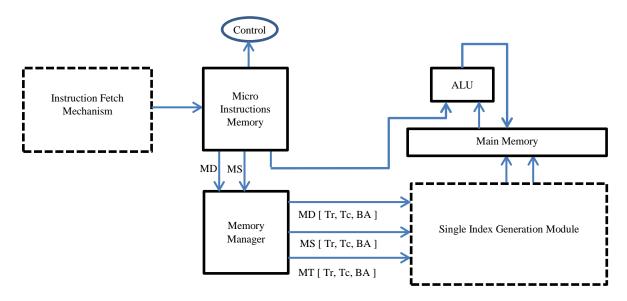

| Figure 5-8 : The micro instruction Fetch Mechanism along the instruction Memory     | . 83 |

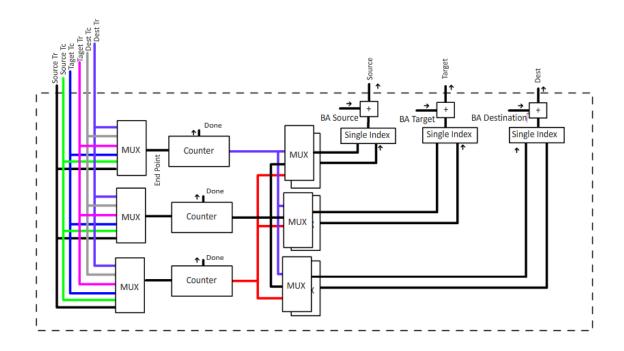

| Figure 5-9 : Data path of the Memory Manager                                        | . 84 |

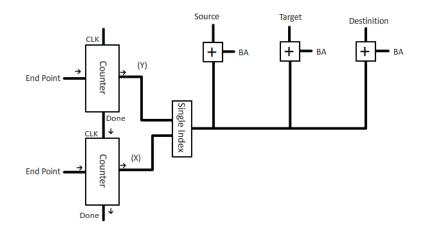

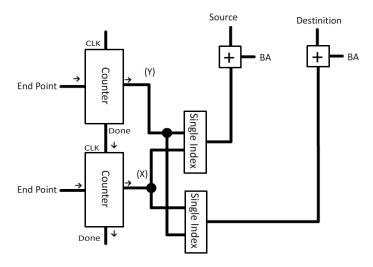

| Figure 5-10 : Index Generation Data path                                            | . 85 |

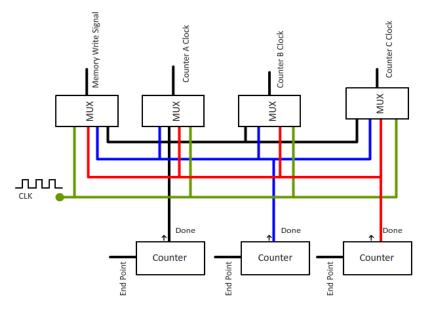

| Figure 5-11 : Clock feeding to Counters                                             | . 86 |

| Figure 5-12 : Data Path for Matrix Addition/ Subtraction                            | . 87 |

| Figure 5-13 : Index Generation for Matrix Addition / Subtraction                    | . 88 |

| Figure 5-14 : Index Generation for Matrix Multiplication                            | . 88 |

| Figure 5-15 : Index Generation for Transpose of a Matrix     | 89  |

|--------------------------------------------------------------|-----|

| Figure 5-16 : Matrix with Scalar Operations                  | 91  |

| Figure 5-17 : Matrix with Scalar Operations                  | 91  |

| Figure 5-18 : Matrix with Scalar Operations                  | 92  |

| Figure 5-19 : Matrix with Scalar Operations                  | 93  |

| Figure 5-20 : Branching and looping                          | 93  |

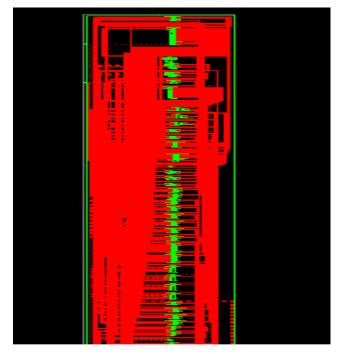

| Figure 5-21 All Data Paths Integrated (main Architecture)    | 95  |

| Figure 6-1 : The configuration file snippet                  | 96  |

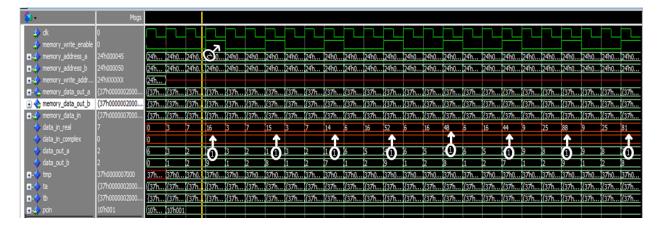

| Figure 6-2 : Wave/Timing Diagram while calculating the DTFT  | 98  |

| Figure 6-3 : Wave Diagram representing Matrix Multiplication | 100 |

| Figure 6-4 : Wave Diagram representing Matrix Addition       | 101 |

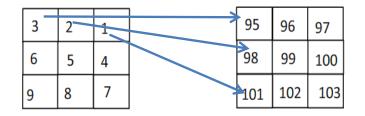

| Figure 6-5 : Actual memory Addresses in liner memory         | 102 |

| Figure 6-6 : Main Memory linear addresses in matrix form     | 102 |

| Figure 6-7 : Mapping of Matrix values to new locations       | 103 |

| Figure 6-8 : Mapping of Matrix Transpose                     | 103 |

| Figure 6-9 : Simulation results for branch                   | 104 |

| Figure 6-10 : Wave diagrams for results                      | 105 |

| Figure 6-11 : View of the instruction memory in HEX format   | 105 |

| Figure 6-12 : Filter generation results                      | 106 |

Pattern recognition has been another challenging segment for man-made marvels, with the passing flow of time, requirements for Luxury and Necessity are demanding more extensive research in the field of pattern Recognition. From above a century mathematicians and scientists have devoted their whole lives to create and improve algorithms that can perform like Human Recognition System or even better. In a daily human life human brain carries out a lot of pattern recognition without even noticing [1], even it is an irregular pattern human recognition system is even then capable of recognizing. The human brain can also handle new situations even if it's an unseen or a new case. Human brain is still capable of categorizing the object based on previously learned similarity and some logic that might be based on experience. We can even categories voices and recognize that what sort of voice is it i.e. the semantics and structure, Human brain is also capable of recognizing different persons be their face features and body language too, But there are some drawbacks also with the human recognition like humans recognition is slow. The other is that scaling is not easy for everyone and in some special cases human recognition is incapable of classifying. Likewise the case of finger print recognition, not all humans can perform finger print matching; only a highly trained person can perform this task but the efficiency and accuracy cannot be compared as of a machine. The Human brain lacks memory, in case of finding a single sample of fingerprint of a person in a large data, it might take an expert from days to even months to match a single print but comparatively a machine can do this job in the matter of seconds to minuets. The domain of pattern classification is involved in various filed of automations and it is being very extensively used in intelligent machines, some common application of Pattern classification are Voice recognition, fingerprint recognition, face recognition, Optical Character recognition (OCR) Object detection/recognition, Bio Medical Applications etc.

Almost everyone is familiar with the long extending benefits and the services of machines to mankind, the benefits that Machines can provide include speed, accuracy,

cost saving and un-tiring service .Many automatic machines uses the concept of pattern recognition. For example a quality check at a high speed conveyor belt on a production line will require a trained eye to monitor the quality efficiently. A machine properly designed can work more accurately and at very high speeds thus cutting down the cost and the bottle neck that human supervision might create comparatively to the machine. With the span of time, the increasing demand for such machines has proved their worth. The processors that are deliberately designed to perform specific tasks are dedicated processors, or in other words are built and designed for specific/dedicated purpose. These processors can perform almost all the basic operations like loops and arithmetic and logical operations. A processor that can perform logical operations like and, or and not and can loop can handle any kind of software related problem.

Security has been man's nightmare from the beginning of time, whether it is an organization or an individual being on the safe side matters a lot .There has been a tremendous increase in the trend on relying on machines to provide self and automated security using vision or sensor systems. A simple camera attached to a machine capable of running a smart algorithm can provide a very effective and low cost security watch and the best part is that unlike human machine never sleeps and it cannot be bribed either, thus can provide a much safer environment. Whether it's the matter of home land security or security of an individual these machines can provide greater services to mankind. In the field of defense modern radar systems are also providing a great deal of protection against enemy trespassing and attacks, there are several issues with old radar systems, one big problem was that they only provided data visually to the human eye, than the fate of the entity to be saved fully relied on the human and brain on the watch. Comparing to human, machines can work more efficiently and the efficiency dose not drop throughout the time as tiredness and boredom can severely effect humans work performance.

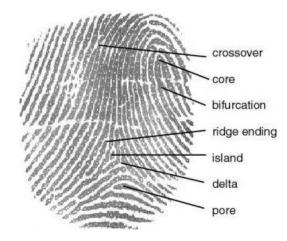

Correlation Pattern recognition has contributed a lot in the field of pattern recognition [1-3]. Usually digital machines are dealing with digital signal, Image and Audio can also be referred as a digital signal and the techniques of pattern recognition can be applied to these digital signals. The main concern is to properly classify an object or an entity so that it can be further worked upon. The following diagram represents some features of a fingerprint scan, features help in logically classify the object.

Figure 1-1: A fingerprint diagram with some salient features [1]

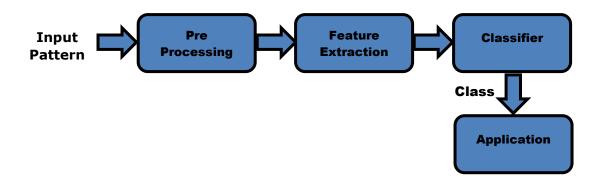

In pattern recognition usually an input is provided to a system, usually a system should perform some preprocessing to adjust the image so that the system can perform operations on the image in a more optimal way like removing the noise the input image that might have been added at the image acquisition phase or allying some algorithm that can enhance classification process. Afterwards the system extracts suitable number of required features and the works on the features of the provided pre-processed input, based on these features a decision is carried out whether to which class the input may belong to. The following diagram explains how a trivial Pattern classification mechanism works.

Figure 1-2: Typical Flow chart for typical Pattern Recognition system.

#### **1.1 Typical Methods:**

Following methods are generally used for recognizing a pattern

- Statistical

- Machine learning

- Artificial neural

- Correlation filters

The above mentioned approaches are mostly carried out in image spatial domain, where more significant advantage can be obtained in Frequency domain. All the input image might not be the same always there might be some sort of illumination changes in the input image, besides illumination there is a chance that multiple repetition of the pattern might occur in the input image, this situation should also be cratered .The desired pattern can exist anywhere in the scene. Another big challenge is that the desired pattern in the image might scale, rotated or translated. There must be an algorithm that that is robust of all the above mentioned problems .Luckily correlation filter can provide efficient and robust pattern classification. Straight forward correlation of test input can be carried out on a reference sample that will result in higher peaks in a correlation plane where the reference image exists.

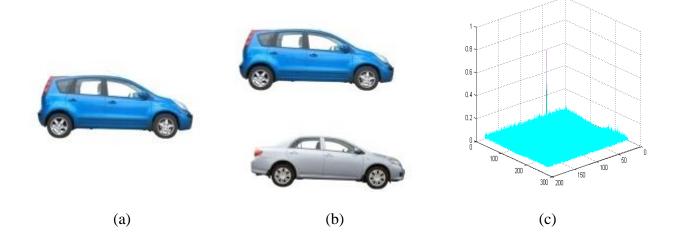

# Figure 1-3: (a) input pattern (b) Reference image (c) Correlation Plane (correlation results of (a) to (b))

The figure shows the correlation results of a test image over a reference image, in the resulting correlation plane the peak indicates the location of the test object in the reference image, sharper the peak the more is the probability of the test object to be present in the reference image. If the image has more than one existence of the test object in the reference image, the peaks will be replicated Straight forward Correlation technique lies under the field of statistics but is quite inefficient, Correlation filters designed in frequency domain have greater advantage of speed thus helping in building real time applications for pattern recognition .

Typically correlation filters are designed in frequency domain, there are many filter that are designed using FFT (Frequency Domain), mostly this technique is employed where Real time processing is required .Like the radar systems are critical, the modern aircrafts have almost broken the sound barrier and can travel up to or more than speed of sound, it is very critical to develop an algorithm that can process the sample gathered by the radar system in real time. If the processing is slow there are very high chances that the aircraft will reach its target unharmed and it might be too late to apply preventive measures.

Correlation filter are developed in frequency domain using the reference inputs, which are basically referred as the training sample or training data. A correlation filter is developed one filter per class, the training data contain the variations of the pattern o be detected, the variations include some rotation of the pattern. There also might be some scaling difference between the training samples. One filter developed results in a correlation plane when it is multiplied (correlated) to a Test input. If the object is present in the reference image it will produce peaks. That refers to the location of the pattern on the reference image. Furthermore algorithms and methods can be used to detect the pattern in the reference image using the obtained peak.

Many correlation filters have been developed with time, with grate performance. These filters include the *synthetic discriminant filter* (SDF) which was among the earlier developed correlation filter. Furthermore known filters like *Maximum Average Correlation Height* (MACH)[4-6], *Extended Maximum Average Correlation Height*

(EMACH)[7, 8], Eigen Extended Maximum Average Correlation Height (EEMACH)[9], Maximum Average correlation energy (MACE)[10], minimum noise and average correlation plane energy (MINACE)[11], Minimum variance Synthetic Discriminant Function (MVSDF) filter [12] etc. These filters are more robust and can perform the recognition at very high speeds.

#### **1.2 Motivation**

Over the years small form factor and power efficient flexible and programmable devices have captured the marked trends, These devices can work at very higher speed .custom built digital designs are more commonly implemented on these flexible hardware. For a mass production of a digital design semiconductor materials based chips are employed, the whole system can be fabricated on these chips these. To manufacture these semiconductor material dyes have to be manufactured first the manufacturing of these dyes itself is an expensive and pain giving procedure, but ultimately this method in mass production cuts down the cost of the digital design.

On the other hand if there is only one custom design that requires fewer amounts of copies to be produced, the simple flexible devices like FPGA, ASIC, CPLD can be employed. Although a single piece of custom design hardware will cost more than a single piece Mass produced hardware, but on the other hand if it is desired to manufacture a single piece of hardware using the mass production strategy that will increase the manufacturing cost at very high level. That is the main reason that the trend toward these flexible hardware has been increasing over the time. These electronic devices allow Design engineers and hobbyist to produce cost effective and very efficient and intelligent electronic devices.

Design Engineers around the world have been employing FPGA, CPLD etc. to implement and test their designs. In the last decade with the availability of FPGA with more memory has motivated the design engineers to also implement the image processing techniques on these devices .These devices can also be programed using *Hardware Descriptive language* (HDL).Some of the manufacture of these devices also provide pre built libraries that are tested and optimal speed wise, some open source languages to describe the design are have also been introduced into the digital design world. Verilog

and VDHL are the most common languages used to program this flexible Hardware. The reasons why Design engineers use these technologies involve their small size, Low power consumption, flexibility and that they are capable of performing at higher speeds compared to a general Computer. Now a days top leading electronics devices manufactures are manufacturing the state of the art devices these days. A single digital camera and a Cellular phone uses up a very powerful processor capable of performing different tasks. The digital cameras these days are using small but simple image processing techniques to attract the customer. Smile and face detection are some examples, these camera are also capable of Enhancing the images using different enhancement techniques like filtering Histogram equalization, these techniques when applied pleases the human eye. The increasing trend in luxury requires more effort to be put into the field of embedded and dedicated systems.

Common correlation filters [1] can be implemented on general computing, but as mentioned in the above paragraphs that in some requirements small form factor devices, less power consumption and speed is a crucial matter. Face and smile detection can also be carried out on a general computer but it not always possible to carry a huge sized general computer. Besides this the correlation filters requires huge amount of computations .Besides this the general computing environment is usually running an operating system, the operating system is handling a lot of demons and application running in the background these applications require a lot of processing power, usually in general computer the processing power is shared among the tasks running on it where n the other hand dedicated hard ware does not require to share resources to other entities. FFT [13] its self is a compute intensive procedure and might cover much hardware cost itself. The discrete time Fourier transform is slower than FFT and also requires large amount of memory even on general computing. The main goal is to provide a very flexible architecture that is capable of performing all the tasks required by a correlation filter design, thus providing a Correlation Pattern recognition module that is flexible and provides great performance.

There are other Hardware Platforms available in the market at low costs that can provide a general computing environment with lesser power consumption, smaller size and the flexibility of a general computer .A simple microprocessor and some DSP Processors [14] can also carry out the tasks required to perform a correlation Pattern recognition application. Besides these devices Raspberry Pi [15] is also providing a small sized ARM[16] based Credit card size Computer with necessary Peripherals. Some other companies are also manufacturing Flexible processors like Cortex, ARM etc.

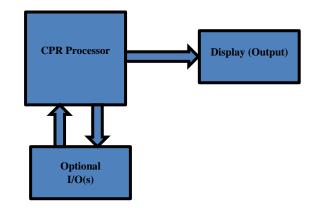

Figure 1-4: A standalone Model for CPR

#### **1.3 Challenges**

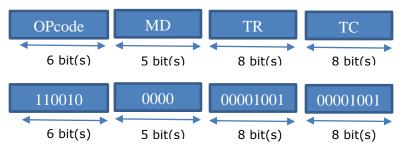

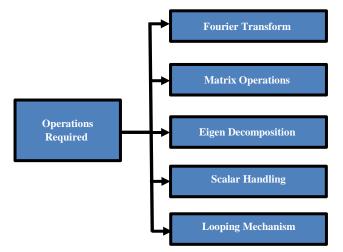

Designing an architecture that is capable of performing correlation pattern recognition requires to perform numerous small tasks that are entirely different in nature .There were several possibilities to realize this type of Digital Design. Some of the challenges faced in this research project are enlisted with some detail.

#### 1.3.1 Flexibility

Most Digital design engineers while designing a dedicated system only focus on certain amount of specifications, for example a system is designed to work on an image of (128 X 128) pixels only .What if the end user has to change the size of the input image to (256 X 256) pixels. This problem has always been a question mark on the digital design industry. A digital design usually has to be replaced if no room is kept to tackle this size of problems. Replacing an old design has then its own requirements that can cost a great deal of time and money.

#### **1.3.2** Cost Effectiveness

Another Big challenge in this case is to provide best performance at low cost. Usually Cost is directly proportional to performance. As the designers try to increase the performance of the machine the cost raises up to i.e. it consumes more hardware [17].

Besides performance, while increasing flexibility of a certain design also increases the hardware costs. It's nothing but a tradeoff which cannot be ignored. In case of EMACH Filter, this filter itself requires a lot of different operations like, Computing Fourier transform, Computing Eigen Values and Eigen vectors, Basic Matrix Operations like Matrix addition, subtraction, Multiplication. These operations themselves are a very big challenge to design individually. Such an architecture that has to perform all of these operations all together while saving cost and providing on chip flexibility is the biggest challenge.

#### **1.3.3** Common Requirements

Many of the operations like finding the Fourier transform, computing the Eigen vector and values requires many operations like addition, subtraction Multiplication etc. If each module is merged together in a logical way the cost of the hardware will raise too much .some of the operations that a correlation filter design may require include .Frequency Domain Conversion (Computing FFT),Inverse Fourier Transform (Computing IFFT),Finding Eigen Values and Vectors, Finding Maximum and Minimum values, Implementation of some Numerical Methods, Maintain orientation of Matrix During operations, Matrix Addition, Matrix Subtraction, Matrix Multiplication (Scalar, Dot, Matrix),Matrix Division (scalar),Representing Complex Numbers scalar/matrix, Representation of conjugates of matrix, Calculating power of a matrix, Calculating Transpose of a matrix, Reshaping of a matrix , Provide a use of fractional Values, Provide Flexibility, Perform Logical Operations and Hazards Identification and removal. All the required parameters are quite challenging.

The above mentioned are the sub tasks that are required by the steps involved in the filter design, and the correlation. Each thing its self is a very big challenge to be implemented on hardware. One other Challenge was to provide these functionalities all to gather while cutting down the hardware size.

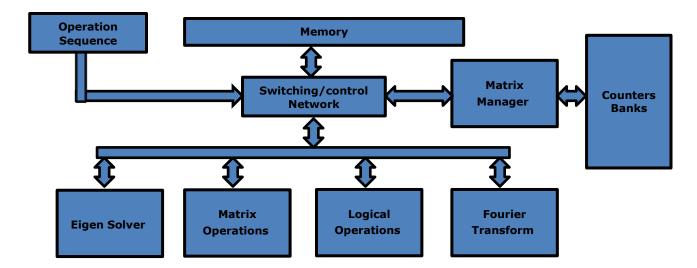

Figure 1-5: Diagram representing the requirements to perform CPR

The figure above shows the required operations to perform a correlation based pattern recognition. This is not the exact estimate but a near estimate that a design would require. This approach involves implementation of each module separately and then integrating the modules via an intelligent switching/Control network, this is one possibility, but to reside all the functional modules on a single chip will rise up the cost to a very large extent. Here one can clearly see the big challenge in the realization of this CPR generic Architecture. Thus it is intended to find common operations used by all the functional units (Subset of Operations) and Produce a design that is more cost effective.

#### **1.4 Previous Works**

Many researchers have contributed to the hardware design for image processing. Previously presented designs were based of different flexible platforms. These platform includes some well know hardware which boosts up image processing speeds. ASIC (Application Specific Integrated Chips), DSP (Digital Signal Processors) and some reconfigurable devices like FPGA (Field programmable Gate Arrays).Many image processing algorithms like edge detection using Sobel's, Prewitt's and canny were implemented on specific hardware implementation to FPGA manufacturers like Altera, Xilinx etc. G.S. Richard [29] presented the idea of generating a parameterized program for convolution filters implemented on FPGA. Filter was constructed using a set of multipliers and adders generated from a canonical serial-parallel multiplier stage. Atmel proposed a 3 by 3 run-time reconfigurable convolution filter on FPGA. F.G. Lorca [30] presented an implementation of filters for 1D and 2D reducing memory usage and computational costs by half in software side and hardware. Nelson [31] presented and implementation of rand order filter, Morphological operations on Xilinx Virtix and Altera Flex 10K FPGA. Shinichi [32] realized the different image processing techniques for computation of image gravity center along with orientation detection using Hough's transform and radial projection. Fahad [33] proposed a high performance pipelined edge detection architecture for real time processing of images. Baran [34] implemented edge detection algorithm coded in impulse, further synthesizing the code for Altera Nios.

#### **1.5 Orientation of Thesis**

The reaming thesis is organized as described below. Chapter 2 contains a brief overview of the literature regarding to the processor, Chapter 3 explains the design and working of the individual components that builds up the processor. Chapter 4 explains the instruction set architecture along ith their use, Chapter 5 shows and explains the data path of different type of instructions, chapter 6 shows simulations results compared with actual results calculated by Matlab.

The design of a digital architecture has a mandatory prerequisite, this is to study the problem thoroughly .The sub-problems of the main problem should be known very precisely to realize the digital version. The digital standalone architecture design of a CPR Processor requires to identify the sub operations and their detailed study.in this chapter an overview of the theoretical study of sub operations are presented.

#### **2.1 Correlation Filters**

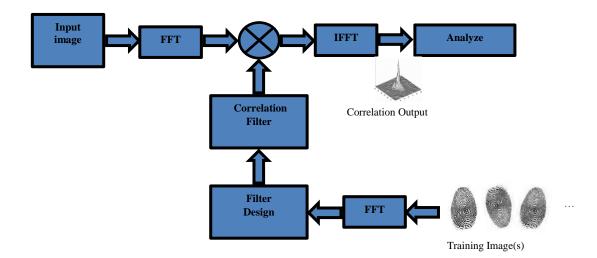

Correlating filter has a significant edge in Pattern recognition due to their shift invariant and shift tolerant nature. Design process of a correlation filter involves the Fourier transform form of that particular image training samples. Fast Fourier Transform is usually employed for conversion from spatial domain to frequency domain. Figure 2-1 represents the common flow of a correlation filter. Some of the correlation filters mathematical back ground is explained in the next section.

Figure 2-1: A Correlation Filter application flow

#### 2.1.1 MACH Filter

MACH Filter is among recently developed filters. The design of this filter maximizes the peak energy using the mean of the training sample of provided image(s).in this section a brief overview of this filter design is presented the detailed version can be found at [5]. Like other correlation filters MACH Filter is also completely designed in frequency domain. The first step in the development of this filter is to compute the Fourier transform of a 2 Dimensional Image (2D Matrix) is computed. The size of one training image is assumed as  $d \ge d$  pixels. For computational ease the results are then converted to column vector, by scanning from left to right. After this the scanning is done from top to bottom sequence. The resulting 2D filter **h** can also be expressed in the same way. The *i*<sup>th</sup> training image's correlation output can be represented by equation (2.1.1)

$$c(0,0) = h^+ x \tag{2.1}$$

Peak intensity of average training image can be expressed by the expression in 2.2, also referred as *Average Correlation Height* (ACH) [5]. The notation **m** represents the Average of all the *Fourier Transforms* (FTs) of all the training images, where the total number of images is denoted by **N**.

$$|\overline{c}(0,0)|^2 = \left|\frac{1}{N}\sum_{i=1}^N h^+ x_i\right|^2 = |h^+m|^2 \qquad (2.2)$$

A tolerance characterizing measure metric Average Similarity Measure (*ASM*) is introduced which basically shows the dissimilarity between correlation output, training images and the average of the training images.ASM can be expressed as follows

$$ASM = \frac{1}{N} \sum_{i=1}^{N} |g_i - f_{opt}|^2 \quad (2.3)$$

Where  $g_i = X_i h^*$  and  $f_{opt} = M h^*$

$X_i$  Represents a diagonal Matrix, the diagonal entries contains the elements of the FT vector along the diagonal. Matrix **M** is also a diagonal matrix that has the elements of **m** along the diagonal. The size of these tow diagonal matrix will be  $d^2 \times d^2$ . Where  $g_i$  represents the correlation output of  $i^{th}$  training image. The term  $f_{opt}$  refers to optimal

reference correlation output resulting in minimum mean square error this is usually found by measuring the gradient of ASM with respect to  $f_{opt}$ . Afterwards the putting the expression equal to zero and solving the expression for  $f_{opt}$ .

By substituting the values of  $f_{opt}$  and  $g_i$  in equation (2.3) will yield the following expression.

$$ASM = h^{+}S_{x}h \qquad (2.4)$$

where  $S_{x} = \frac{1}{N}\sum_{i=1}^{N}(X_{i} - M)^{+}(X_{i} - M) \qquad (2.5)$

Up till here  $S_x$  is a diagonal matrix with size  $d^2 \ge d^2$ . The small x in the subscript of the equation (2.4) indicates the dependence on the training image of a certain class x. By using equation (2.4) and (2.2) will result in equation (2.6) shown below.

$$J(h) = \frac{|\overline{c}(0,0)|^2}{h^+ I h + h^+ S_x h} = \frac{h^+ m m^+ h}{h^+ (I + S_x) h}$$

(2.6)

Noise also has a role in the images which usually adds at the input, the term  $\mathbf{h}^+\mathbf{lh}$  represents the *output noise variance (ONV)* [18]. This makes this system noise tolerant. The filter is then computed by taking the gradient of equation (2.6) w.r.t.  $\mathbf{h}$  and afterwards putting the expression equal to zero. The resultant is given in the following equation

$$h = (I + S_x)^{-1}m \qquad (2.7)$$

In the above section MACH filter was described theoretically, this filter has its own limitations. The design of this filter over depends upon the mean of the training images (Mean of FTs). The mean of the images results in loss of some small and important details which are necessary for a good clutter rejection. Mean of the training images results in another clutter image which is quite different from original image [5].

#### 2.1.2 EMACH Filter

EMACH filter is among the modern Developed filter of this era. The over reliance on the average training images in MACH filter lead to the development of Extended Maximum Average Correlation Height (EMACH) Filter which introduced a new a new metric value *All Image Correlation Height* (AICH) [5].

$$AICH = \frac{1}{N} \sum_{i=1}^{N} |h^{+}x_{i}|^{2} - \alpha |h^{+}x_{i}|^{2} \quad (2.8)$$

The range of the parameter  $\alpha$  lies between 0 and 1. This parameter helps in controlling the emphasis on a training image individually. The above mentioned equation can be re written as follows after substituting $\alpha = 2\beta - \beta^2$ , where the value of  $\beta$  lies between 0 and 1.

$$AICH = \frac{1}{N} \sum_{i=1}^{N} |h^{+}x_{i} - \beta h^{+}m|^{2} = h^{+}C_{x}^{\beta}h$$

(2.9)

Where

$$C_x^{\beta} = \frac{1}{N} \sum_{i=1}^{N} (X_i - \beta M) (X_i - \beta M)^+$$

(2.10)

In equation (2.9) AICH becomes the mean of the peak intensities in the correlation of the **N** Training Images. The MACH filter treated the training images as exemplar, but in this case an exemplar is expressed by  $(x_i - \beta m)$ . To match the correlation out puts of all training images as well another metric *Modified Average Similarity Measure* (MASM)[8] is introduced which is defined as follows

$$MASM = \frac{1}{N} \sum_{i=1}^{N} |g_i - f_{opt}|^2$$

(2.11)

Where

$$g_i = (X_i - \beta M)h^* \text{ and } f_{opt} = (1 - \beta)Mh^*$$

(2.12)

Solving the equation (2.4) Yields as below,  $f_{opt}$  is determined by using the method described in section 2.1.

$$MASM = h^+ S_x^\beta h \qquad (2.13)$$

where

$$S_x^{\beta} = \frac{1}{N} \sum_{i=1}^{N} (X_i - (1 - \beta)M)^+ (X_i - (1 - \beta)M)$$

(2.14)

By minimizing the value of MASM the system becomes more tolerant towards distortion .This minimization allows the transformed  $i^{th}$  training image to resemble more to the reference images (transformed exemplars).Conclusively the EMACH filter should maximize AICH value while minimize the MASM value. Also adding the noise (ONV) to the denominator to carter the effect of noise, the following expression is obtained [5].

$$J(h) = \frac{AICH}{ONV + MASM} = \frac{h^+ c_x^\beta h}{h^+ (l + S_x^\beta)h} \qquad (2.15)$$

After saving the above expression using gradient with respect to h the following expression is concluded.

$$(I + S_x^{\beta})^{-1}C_x^{\beta} = J(h)h$$

(2.16)

Where **J** (h) is the Eigen value and h is the Eigen vector of the matrix  $(I + S_x^{\beta})^{-1}C_x^{\beta}$

#### 2.2 The Fourier Transform

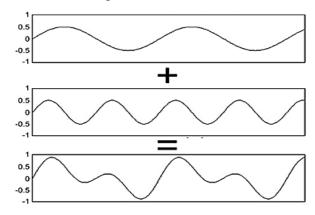

A mathematician named Joseph Fourier introduced a method for inter conversion of signals between spatial domain and frequency domain. This basically a transformation .The best beauty of this transformation is that it is a reversible transform. This method has provided many services in the field of engineering and Physics.

Fourier claimed that a signal can be represented as an ordered (by Frequencies) sum of complex sinusoidal. These sinusoidal can be of different frequencies. The Fourier

transform basically gives the information of frequencies present in a signal, which is quite helpful in analyzing the signal in another perspective. A signal can exist as a sum of sine waves as shown in the next diagram.

Figure 2-2 : Signal represented as a sum of sinusoidal [13]

For a continuous signal, mathematically this transformation can be written as

$$\hat{f}(\varepsilon) = \int_{-\infty}^{\infty} f(x) e^{-2\pi i x \varepsilon} dx \quad (2.17)$$

*Discrete Time Fourier Transform* (DTFT) is used to convert Discrete Values of a spatial domain signal to frequency domain signal. DTFT has a very large number in practical applications these days [1]. In time domain any physical quantity or signal is a function that is sampled among time. An image in time domain contains pixel intensity among a row or column of a matrix. DTFT of a vector can be calculated using the following expression

$$X_k = \sum_{n=0}^{N-1} x_n e^{-i2\pi k_N^n} \qquad K = 0, 1, \dots, N-1 \quad (2.18)$$

In the above mentioned expression  $X_k$  is the Fourier transform value for  $K^{th}$  element place of the resulting Fourier transform vector. The sign -i is a complex number representation,  $x_n$  is the  $n^{th}$  element of the vector. The inverse Fourier transform can be obtained using the inverse calculation expression as follows.

$$X_k = \sum_{n=0}^{N-1} x_n e^{-i2\pi k \frac{n}{N}} \qquad K = 0, 1, \dots, N-1$$

(2.19)

The expressions mentioned in the above section are capable of inter conversion of a 1D array (vector) .But in practice image is a 2D array .the following expression can be used to calculate the DTFT and the inverse DTFT of a multidimensional array[19].

$$\hat{h}(k,l) = \sum_{n=0}^{N-1} \sum_{m=0}^{M-1} e^{-i(\omega_k n + \omega_l m)} h(n,m)$$

(2.20)

$$h(n,m) = \frac{1}{NM} \sum_{n=0}^{N-1} \sum_{m=0}^{M-1} e^{i(\omega_k n + \omega_l m)} \hat{h}(k,l)$$

(2.21)

Although DTFT Provides Fourier transform of the signal, but the method is too slow for computation .DTFT has a complexity of  $N^2$ , later faster algorithms were developed. *Fast Fourier Transform* (FFT) is a method developed with much lower complexity than DTFT .The complexity of this method was reduced to  $N \log_2 N$  which is much lighter and faster the DTFT. This method is considered as the most important Algorithm of all time [20].A detailed explanation of FFT can be found at [21].

#### **2.3 Fourier Transform Matrix Representation**

As described in the above section, the Fourier Transform of a discrete signal can be computed using a summation operator and thus yielding a single value off Fourier Transform for the required Point k. The point to be noted here is that this single value of the  $K^{th}$  Fourier Value has the effect of all the values present in the given vector. Similarly the Fourier Transform (Discrete) of N Points can be represented in the form of a matrix, When this Matrix is multiplied by an input signal it yields the DTFT of the input signal Vector. To compute the DFTF of N Points signal the transformation matrix will have  $N \times N$  elements.

The DTFT Calculation can be performed as X = Wx where X is the resultant Fourier Transform, W is the DTFT Transformation matrix and x is the vector of which the DTFT is to be computed using For a vector with N points the transformation matrix of size  $N \times N$  can be represented in the following way.

$$W = \left(\frac{\omega^{jk}}{\sqrt{N}}\right)_{j,k=0,\dots,N-1} \quad (2.22)$$

The value  $\omega = e^{-\frac{2\pi i}{N}}$  represents the primitive  $N^{th}$  root of unity, also a complex value that is  $i = \sqrt{-1}$  and  $1/\sqrt{N}$  is the normalizing factor.expanding the above equation in the matrix form can be represented as.

$$W = \frac{1}{\sqrt{N}} \begin{bmatrix} 1 & 1 & 1 & 1 & \cdots & 1\\ 1 & \omega & \omega^2 & \omega^3 & \cdots & \omega^{N-1} \\ 1 & \omega^2 & \omega^4 & \omega^6 & \cdots & \omega^{2(N-1)} \\ 1 & \omega^3 & \omega^6 & \omega^9 & \cdots & \omega^{3(N-1)} \\ \vdots & \vdots & \vdots & \vdots & \vdots \\ 1 & \omega^{N-1} & \omega^{2(N-1)} & \omega^{3(N-1)} & \cdots & \omega^{(N-1)(N-1)} \end{bmatrix},$$

(2.23)

Multiplication of this matrix with, a *N* point vector will yield the DFT of the input vector. This technique can be employed for computation of DTFT like a stored table. To find the inverse DTFT the sign of the exponent can be reverse to find the Inverse Transform another way to compute the inverse DTFT is to multiply the matrix with the conjugate of the transformation matrix x = WX.

An image is represented as a matrix or a 2D vector for the case of images the same mechanism can be employed to calculate the Fourier transform of images. In general first the Fourier transform can be computed using the DFT equation. The resulting Matrix is transposed and again the Fourier transform is computed and then again the transpose of the resulting is the final DFT of the 2D matrix.

$$X = DFT(DFT(x)^{Transpose})^{Transpose}$$

(2.24)

Similarly by Matrix Multiplication the Fourier Transform of a 2D Matrix (image) can be computed in the following manner.

$$X = W \times W \quad (2.25)$$

38

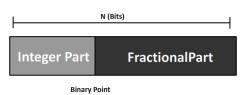

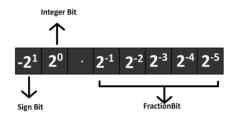

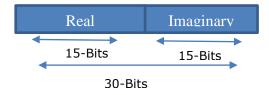

#### 2.4 Fixed Point Representation of Binary Numbers

In real life problem mathematical numbers usually have a fractional part, for example to represent a number half can be expressed by adding a fractional part after a decimal point. i.e. (1/2=0.5).Fixed point is a simple and easy way to represent Fractional numbers in binary representation for a machine.[22] Another way to represent fractional numbers is the Floating point Method which is capable of representing fractional numbers with a good precision. The floating point representation will require a separate hardware or module for conversion i.e. Floating Point Unit (FPU). In many of the cases speed is more critical than accuracy. Fixed point representation can be used in such cases to represent fractional numbers in binary. In old computers the calculations were only done on integers, and programmers used a software based method to deal with fractional numbers [23].Fractional part of a number falls between 0 and 1, in digital signal processing the use of real number is essential. The fixed point Binary number representation is a light weight method in terms of speed and hardware requirements. This method can also be employed in the digital design of a certain application where representation of real numbers is mandatory.

The binary point remains stationary at the same position where the number of binary digits in each word remains the same. In the case of floating point, position of the decimal point is determined at the time of processing. As compared to the fixed point, Floating point has much greater range of numbers that it can expressed. For fixed point representations m bits can be used for the whole part and n bits can be used for the fractional part this is also refers as Qm.n format.

Figure 2-3: Word Representation of fixed point binary [22]

The total number of bits required to express the real number will be the number of bits of the Whore part plus the Number of bits used to represent the fractional part. For example a Q3.3 where m and n are equal to 3, the number of bits required to express the number will be 6.To represent a fractional number two parts are required, the integral part and the fractional part. The integral portion can be signed or unsigned .The following representation shown for signed and unsigned numbers.

An N-bit(s) Fixed Point Number in binary can be interpreted as an integer or a fractional number .For example for an unsigned 4-bit number with Q2.2, 2bits Integer part and 2 bits for fractional part. "0100" represents a fractional number 1.0, where as if it's viewed as an integer it represents 4.

Figure 2-4 : Representation of fixed point numbers

# **Chapter 3 Implementation**

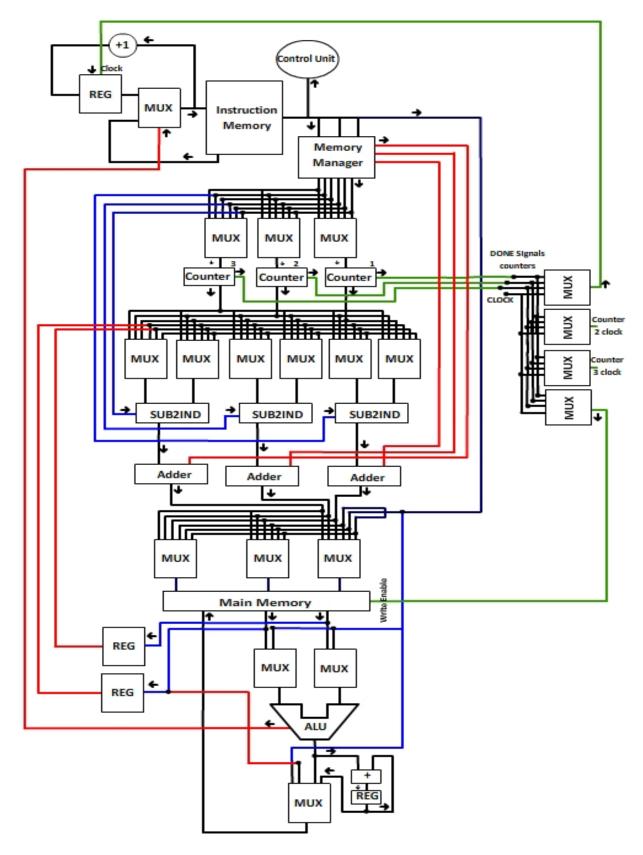

As described in the previous chapters, functional requirements for realizing a CPR processor. In this chapter the implementation and reasons of the modules is explained in detail. As the nature of major operations required to calculate the filter are far different from each other, it is then feasible to cut out basic operations and implement them in such a manner that the functional parts can be reused over and over instead of integration standalone modules, in this way the flexibility of the modules can be retained . For example the Fourier Transform conversion requires the addition and subtraction operation, whereas the calculation for Eigen vectors and values also requires an Adder and Subtractor. It is possible that we can use a single module for Addition and Subtraction and impose some control instructions through which operations can be controlled. The internal Architecture of the components is not added because of intellectual property of the author. The modules are further used to construct a processor capable of performing many complex computations on hardware.

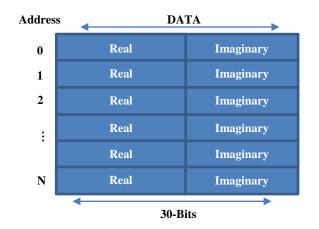

#### 3.1 Main Memory

The main memory is basically simple memory that is designed to hold the contents of the matrix. The memory is liner in nature .It can be assumed of an array holding the contents without any logic or in other words the items or elements are place randomly, the memory will be un familiar that to which matrix the elements belongs to. For example the memory is kept of 64 Kbytes.it means that we can store 64 Thousand values with the width of 1 Byte (8-Bits).Suppose we are need to store 2 matrix of size 3 x 3 in this memory, the values will be stored in a continuous manner.

$$A = \begin{bmatrix} A1 & A2 & A3 \\ A4 & A5 & A6 \\ A7 & A8 & A9 \end{bmatrix}, B = \begin{bmatrix} B1 & B2 & B3 \\ B4 & B5 & B6 \\ B7 & B8 & B9 \end{bmatrix}$$

| Memory Address | Content |

|----------------|---------|

| 0              | A1      |

| 1              | A2      |

| 2              | A3      |

| 3              | A4      |

| 4              | A5      |

| 5              | A6      |

| 6              | A7      |

| 7              | :       |

| 17             | B8      |

| 18             | B9      |

|                | :       |

*Figure 3-1: Elements of two Matrices placed in same memory (a memory overview)*

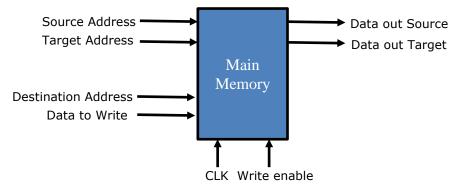

In general computing the memory is usually managed by the operating system, this management is transparent to the user. In case of this processor a liner memory will be used and the management of the memory will also be transparent to the end user .The user will only have to write the micro instruction like "ADDm C, A, B", The user will only specify whether he wants to add a scalar value or a matrix point to point. There are many orientations of memory that can be used, a dual port read memory design like a MIPS32 processor has a register file with output ports of data and three input port for address, another port for data input plus some Control pins like read write control. In this case a similar type of memory will be used, the major benefit of this memory is that it can provide two operands and a target location and can complete one instruction in a single cycle. The main aim is to keep the processor work in a single cycle per micro instruction. The memory layout is shown in the following diagram with its detailed pin in and pin out. R/W shows the read or writes signals. The contents of the memory are in mixed format, it will store fixed point representation and binary point representation together.

Figure 3-2 : Main memory module layout

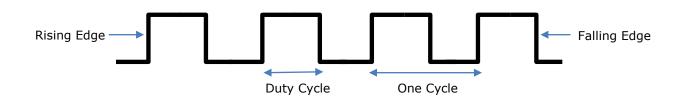

The source and target address fetches from the same common pool of memory at the same time, and the write data will write to the same pool of memory at the address specified on the destination address port. The memory is restricted to one operation at an edge of clock cycle. The Memory is restricted to read on the rising edge of the clock cycle and allowed to write at the falling edge, this methodology is adopted to avoid hazards that will be discussed later.

Figure 3-3: Description of common features of clock cycle.

To write the memory the write enable must be set to '1', then on the negative edge of the clock cycle with write enable at set position the Data available on the data input will be written to the destination address. The size of the address in bits depends on the memory size, for a memory of sized N requires an address line of  $log_2(N)$  bits. For example a memory of 32 Locations will require an address of  $log_2(32)$  bits, which is 5 bits. Thus to access a memory of 32 locations will require a 5 bit wide address line. Images usually have large number of pixels. Each pixel is a gray scale value at a certain row, column of a matrix location. As an image is represented by a large sized matrix, therefore to serve the purpose of image processing application a large amount of memory will be required. For example to store 8 gray scale images of sized 64 x 64 pixels, the depth of memory require will be (8x64x64), which is 32768 locations, the width of the memory will be 8bits for a gray scale image. So the total amount of memory required will be 32,768 Bytes of 262,144 bits. This is very large amount of memory. The address bus required for this memory size will be  $log_2(32768)$  which 15 bits is. A detailed mechanism of saving and reusing memory will be providing in chapter 5.

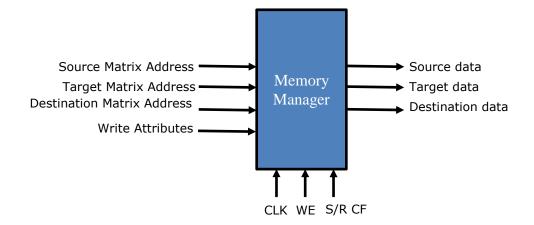

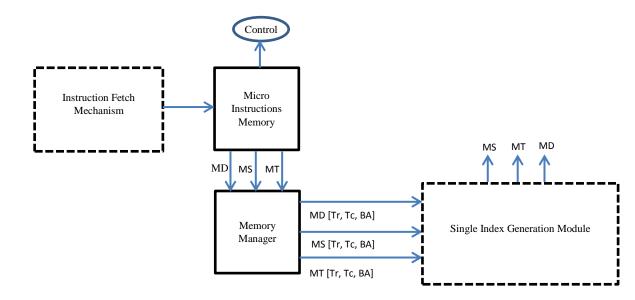

#### **3.2 Memory Manager**

To provide flexibility to the processor and ease of use to the user an on chip mechanism is adopted to provide the dynamic control of functionality. In terms of image size we need to specify a size of image that will allow the processor to learn that what image size it is working on. A module named memory manager is introduced to the design. This module is basically a lookup table that can hold three type of information about a matrix. It will hold the base address of the matrix, the total Number of rows and column of a matrix. The memory manager will also provide the ease of micro programming. The instructions and guidelines to the working of the processor will be flexible.

In a general code matrix handling mechanism could be written on the software side, but addition of this functionality will cost more in terms of CPU cycles as the number of decisions and comparisons will be increased, in general computing the main memory of the RAM is the major bottle neck, anything that requires to fetch something from the memory for an arithmetic use or a logical use can cost many machine cycle, some General computing systems even uses cache and virtual memory, in such a case where the required memory location is not available on the cache it will cost even more cycles to fetch, the beauty of the dedicated systems is that custom designs can overcome these limitations hence providing more performance, but in some cases the cost in terms of silicon may rise up to a very great extent. A mechanism for conversion of matrix from its subscript index to a single index is adopted in the realization of this processor the detailed reason for using this mechanism is explained in the next section. The processor provides an on chip mechanism for handling matrices, for this purpose a sparse memory will be used .the layout of this small sized memory is explained below and the module is shown in the figure.

Figure 3-4: Layout of memory manager inputs and outputs.

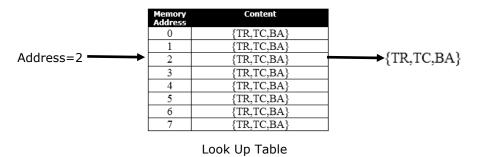

Suppose that the requirement is to store 8 matrices in the memory of size(m, n), the height of this memory will be 8, and the address lines must be of 3 bits. Memory manager is a form of a lookup table which can be written by setting the Write Enable to '1' on the negative edge of the clock .The data will be accessed from a common pool and will be available on the outputs. In the figure shown below the working mechanism of the this module is shown, an input address is 2, the module will output the data available on the address location 2, The second location points to the properties of Matrix Number 2, i.e. *Total Rows* (TR), *Total Columns* (TC) and *Base Address* (BA).

Figure 3-5 : Working Mechanics of Memory Manager

The total size (in bits) of the width of single row in memory manager is the sum of Total Bits (TR) + Total Bits (TC) +Total Bits (BA). The base Address is determined on chip, The base address of the first of size 3x3 matrix stored in the linear memory will be kept to zero. The base address of the second of size  $3 \times 3$  matrix stored in the memory will be

.Kept 9, indicating the elements of the second matrix is starting from the ninth location in the memory.

$$A = \begin{bmatrix} A1 & A2 & A3 \\ A4 & A5 & A6 \\ A7 & A8 & A9 \end{bmatrix}, B = \begin{bmatrix} B1 & B2 & B3 \\ B4 & B5 & B6 \\ B7 & B8 & B9 \end{bmatrix}, C = \begin{bmatrix} C1 & C2 & C3 \\ C4 & C5 & C6 \\ C7 & C8 & C9 \end{bmatrix}$$

Data A1 A2 A3 A3 A4 A5 A6 A7 A8 A9 B1 B2 B3 B4 B5 B6 B7 B8 B9 C1 ...

Address 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20

Therefore a base Address Base Address

Figure 3-6: Linear storage of matric in memory showing their base addresses

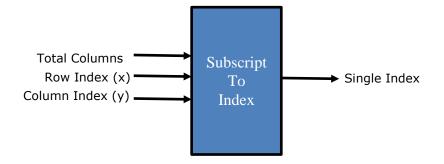

#### 3.3 Sub to Index

As explained in the above section that we are going to use a linear memory that will contain all the matrix placed all to gather without any boundary marking, the module memory manager will hold the information about the marking, that what is what on the main memory. The mechanism is that an element is a matrix can be addressed by its location number. The following will explain the location index of a matrix. Trivially an element of a matrix can be expressed by A(x, y) where x is the row index and y is the column index this is usually known as the sub-script notation of an element, this unique element can also be represented by a unique index A(Z).

In other words it can be written as A(x, y) = A(Z), let us consider an example of a below 3 x 3 matrix. Given a matrix A with values as given below

| $A = \begin{bmatrix} A(1,1) \\ A(2,1) \\ A(3,1) \end{bmatrix}$ | A(1,2)<br>A(2,2)<br>A(3,2) | $\begin{array}{c} A(1,3) \\ A(2,3) \\ A(3,3) \end{array}$ |  |  |  |  |  |  |

|----------------------------------------------------------------|----------------------------|-----------------------------------------------------------|--|--|--|--|--|--|

| (a)                                                            |                            |                                                           |  |  |  |  |  |  |

| $A = \begin{bmatrix} A(1) \\ A(4) \\ A(7) \end{bmatrix}$       | A(2)<br>A(5)<br>A(8)       | $A(3) \\ A(6) \\ A(9) \end{bmatrix}$                      |  |  |  |  |  |  |

| (b)                                                            |                            |                                                           |  |  |  |  |  |  |

| $A = \begin{bmatrix} A(1) \\ A(2) \\ A(3) \end{bmatrix}$       | A(4)<br>A(5)<br>A(6)       | $A(7) \\ A(8) \\ A(9) \end{bmatrix}$                      |  |  |  |  |  |  |

|                                                                | (c)                        |                                                           |  |  |  |  |  |  |

Figure 3-7: (a) Representation of Matrix in Subscript (b) Single index representation (row oriented) (c) Single index representation (column oriented)

The benefit of using the index notation is that we can put all the items of a matrix in a continuous order even in a straight memory and can address the element with index representation. To explain the concept in a more feasible let us consider the example of MATLAB function **sub2ind** (x, y). This function converts the subscript i.e. the row column value to a single index.

| 1,1 | 1,2 | 1,3 |  | 1 | 4 | 7 |

|-----|-----|-----|--|---|---|---|

| 2,1 | 2,2 | 2,3 |  | 2 | 5 | 8 |

| 3,1 | 3,2 | 3,3 |  | З | 6 | 9 |

Figure 3-8: Conversion of Subscript index to Single Index

To realize this conversion a methodology was adopted. The expression which helps in converting the subscript values to single index values. Mathematically the methodology can be written as.

$$A(x, y) = A(Z) = A(((x - 1) * A_{TC}) + y) \quad (3.1)$$

$$Z = ((x - 1) * A_{TC}) + y) \quad (3.2)$$

(a) Row Oriented

$$A(x, y) = A(Z) = A\left(\left((y-1) * A_{TR}\right) + x\right) (3.3)$$

$$Z(((y-1) * A_{TR}) + x) \qquad (3.4)$$

$$(b) Column Oriented$$

The expression (a) can be used to compute the single index in row orientation and the expression (b) can be employed to calculate a single index in column orientation like MATLAB. A simple MATLAB simulation code is presented here to justify the index conversion, the first provided code work in Row orientation and the second sample code works in a column oriented manner.

```

% simulating for subscript to single index conversion

% Author Abdullah Aman Khan

% 01 - January -2013

% Specify the total number of row and col for a random matrix

TR=3;

TC=3;

Matrix=rand (TR, TC);

% Setting Up a loop that will traverse thorough all the values of

the Generated Random Matrix

for x=1:TR

for y=1:TC

single index= ((y-1)*TR)+x;

element subscript=Matrix (sub2ind([TR TC],x,y))

element single index=Matrix (single index)

end

end

```

```

% simulating for subscript to single index conversion

% Author Abdullah Aman Khan

% 01 - January -2013

% Specify the total number of row and col for a random matrix

TR=3;

TC=3;

Matrix=rand (TR, TC);

Matrix tp=Matrix';

% Setting Up a loop that will traverse thorough all the values of

the Generated Random Matrix

for x=1:TR

for y=1:TC

single index= ((x-1)*TC) + y;

element subscript=Matrix (sub2ind([TR TC],x,y))

element single index=Matrix tp(single index)

end

end

```

Figure 3-9: Conversion of Subscript index to Single Index

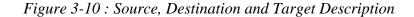

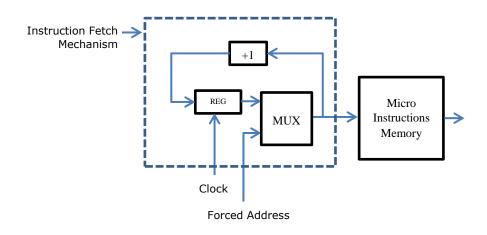

#### 3.4 Sequence Guide

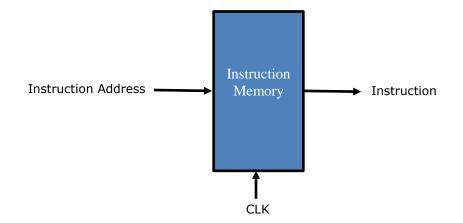

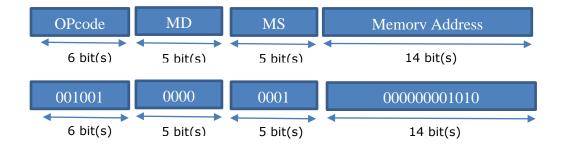

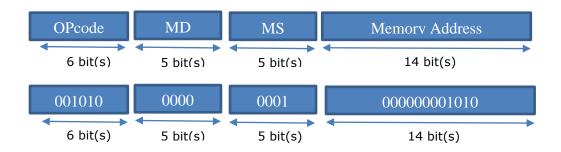

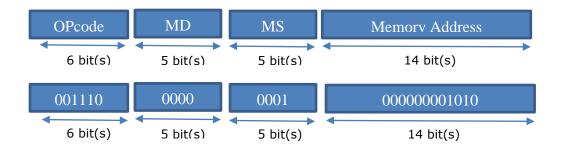

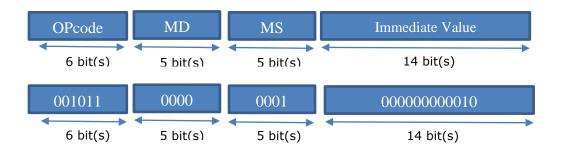

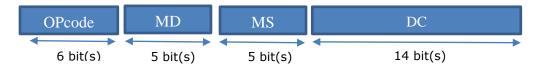

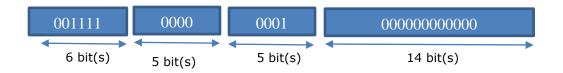

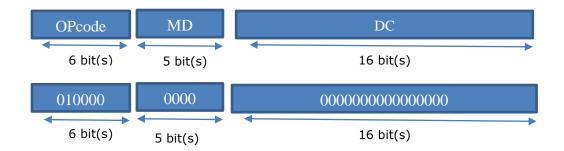

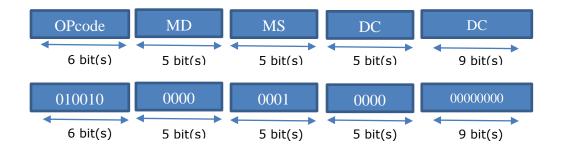

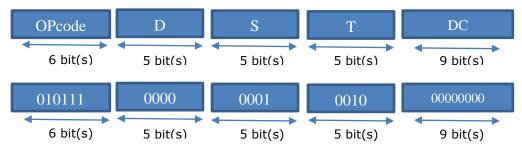

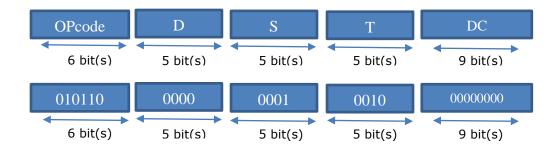

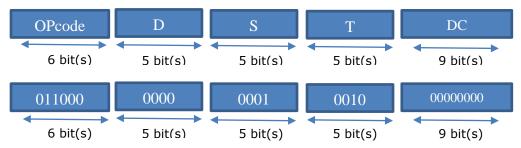

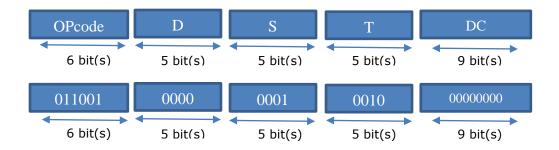

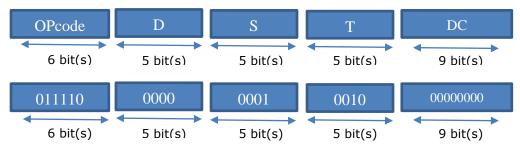

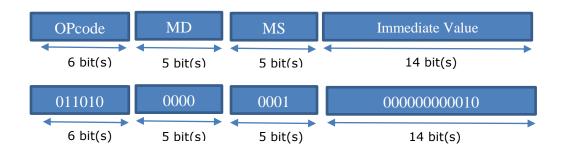

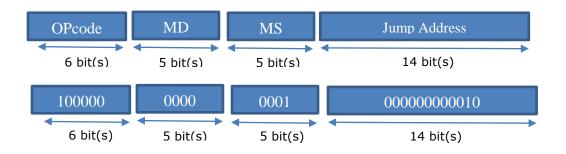

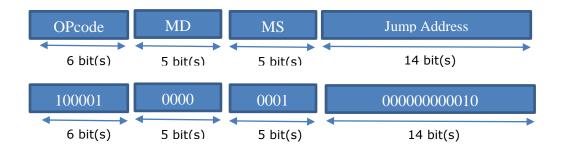

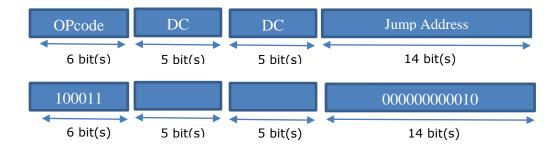

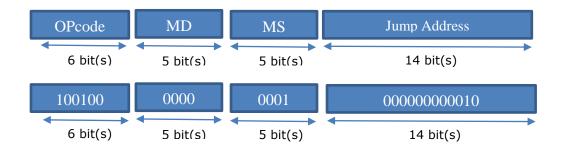

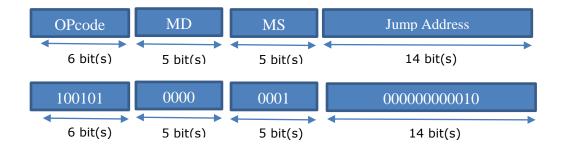

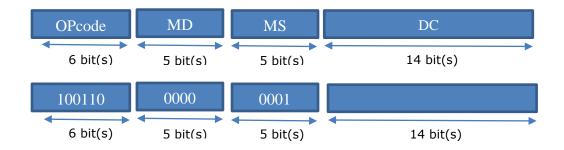

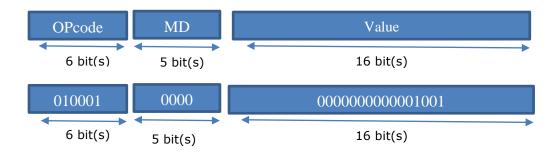

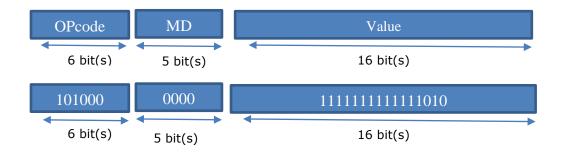

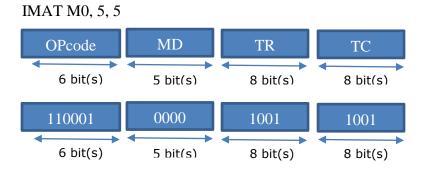

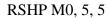

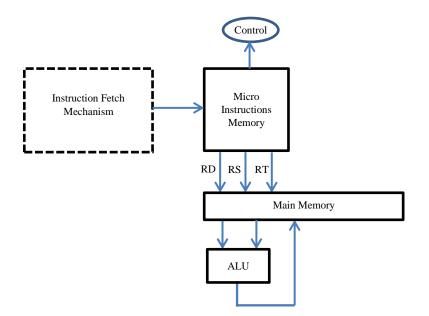

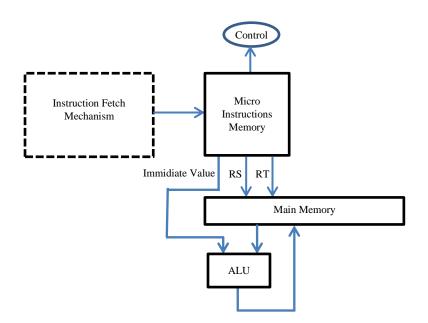

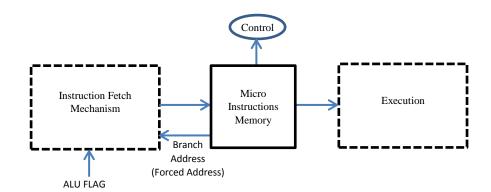

Sequence Guide is a type of instruction memory [24] that contains the instruction or operation to be carried out; one slice or a row contains the OPcode, the Source,

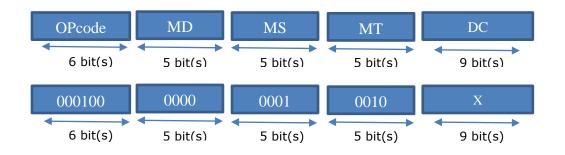

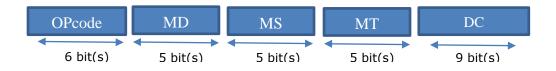

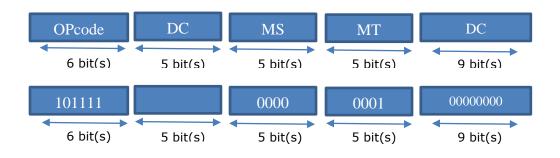

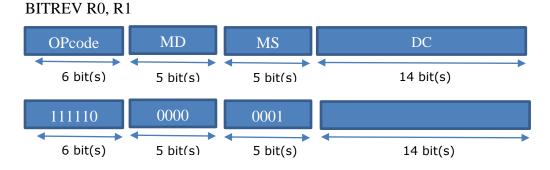

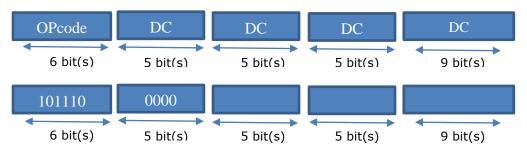

Destination and the target Identifier of the matrix / scalar to be worked upon. The OPcode allows differentiating between the types of instructions according to which the control sequence will be generated. The nature of the instruction can be different from other. The types of instruction are explained in chapter 4. The flow control of a sequence is controlled by special register *Program Counter* (PC). The size of the Program Counter Register depends upon the Height of the instruction memory .Suppose if the height of the Instruction memory is 128 Locations, then the PC register size will be  $log_2(128) = 7$  Bits. The operating mechanism of this guide is similar to the memory manager. MD is the Destination Matrix, MS is the Source Matrix and MT is the Target matrix.

$$A = \begin{bmatrix} A1 & A2 & A3 \\ A4 & A5 & A6 \\ A7 & A8 & A9 \end{bmatrix}, B = \begin{bmatrix} B1 & B2 & B3 \\ B4 & B5 & B6 \\ B7 & B8 & B9 \end{bmatrix}$$

C = A + B

Destination = Source + Target

*Figure 3-11 : The Operation Guide Contents view (Matrix Arithmetic)*

The program counter old the address of the current instruction to be carried out. When a single instruction is executed the address of the next instruction is stored on the PC register, thus allowing a flow of instruction in a sequence. The inputs and outputs of the module are described in this section.

Figure 3-12: The Operation Guide Contents view

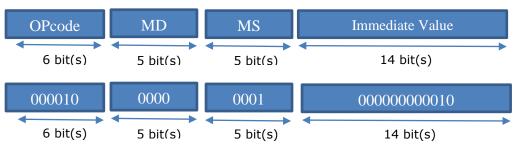

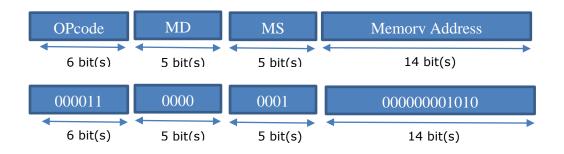

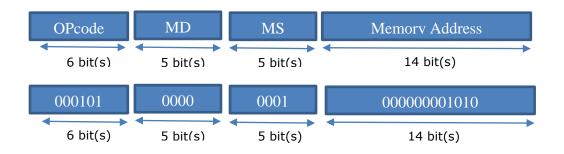

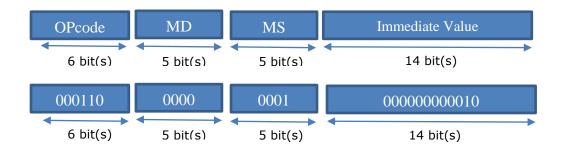

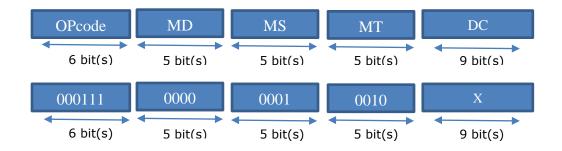

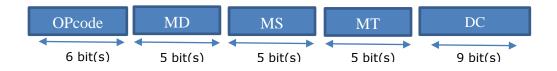

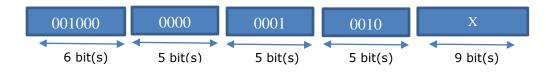

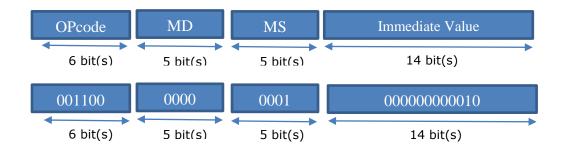

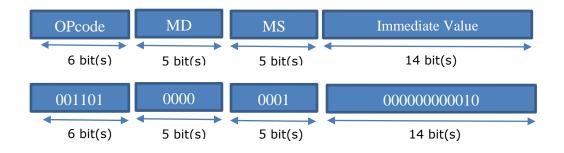

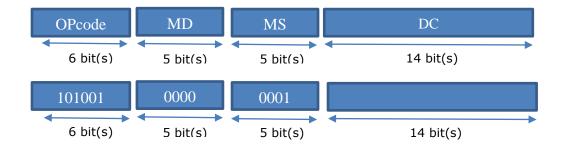

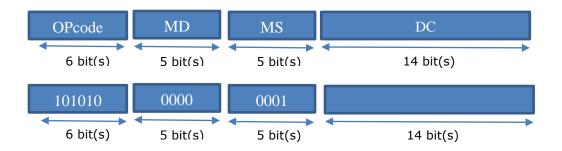

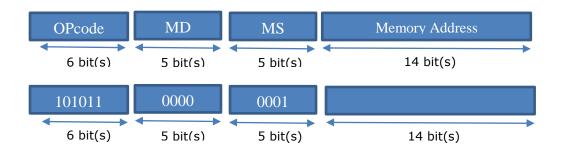

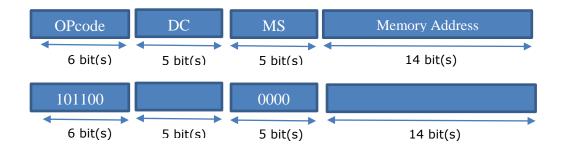

The instruction can be broken accordingly, The Size of the MS, MT and MD depends upon the Height of the memory manager. The memory manager size is kept 8 then the size of the MS, MT and MD will be kept  $log_2(8) = 3$  bits per field. The size of the OPcode depends upon the number of instruction types, if there are 64 types of instructions the size of OPcode will be  $log_2(64) = 6$  bits. The outputs of the instruction memory will be in binary. The total size of the (width) instruction will be then 15 bits.

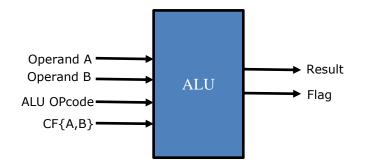

#### 3.5 Arithmetic and Logic Unit

To provide a re-use mechanism of the functional components a central unit is introduced which contains the main adder and is capable of performing logical decisions. The arithmetic and logic unit has two outputs, which are single elements. Arithmetic and Logic operations can be carried out on these operands.

The ALU OPcode identifies that what type of operations are to be performed on the operands, It can be logical or arithmetic like Add, Subtract, Divide .The ALU performs Arithmetic and logical operation on Fixed Point Binary (complex) and Simple Binary (complex) Notations .The Processor requires to operate on Simple Binary Numbers and Fixed Point Binary Numbers Together, The interpretation is different but the arithmetic operations resemble in nature. Fast Adders can be implemented to minimize the delay .Similar components can be internally Implemented to maximize the throughput. This module is a combinatory circuit; it is not dependent on clock cycles.

Figure 3-13 : Layout of the ALU

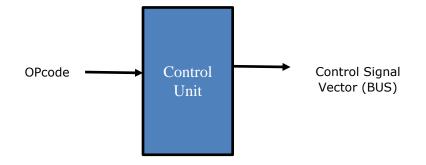

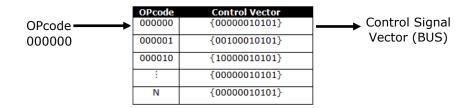

#### **3.6 Control Unit**

The control Unit will dispatch the concerned control signals based on the nature of instruction in use .This dispatch of instruction is based on the OPcode. The Control Unit is also a combinatory circuit, it is also a combinatory circuit and it is not dependent on clock cycles. It is a like a look up table that will output the corresponding set of control vector, the control signals then will be supplied to the to the corresponding fictional unit in the architecture.

Figure 3-14: Control Unit layout

The control Unit operates like a lookup table, the control vector corresponding to the given OPcode will be available on the bus.

*Figure 3-15 : Inside view of the lookup table for Control Panel*

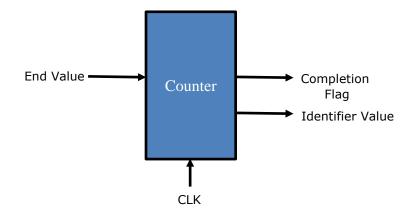

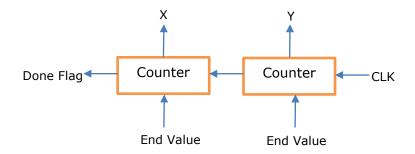

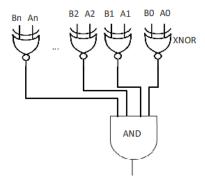

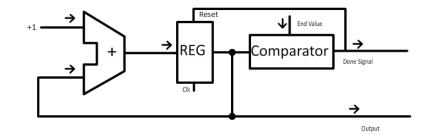

#### 3.7 Counter and Counter banks