# **MOBILE VIDEO SURVEILLANCE**

By

NC Zainab Khalid NC Zunaira Sajjad NC Samoona Aslam NC Jovaria Maqsood

Project Supervisor Lec Intisar Rizwan-i-Haque

Submitted to the Faculty of Electrical Engineering, Military College of Signals National University of Sciences and Technology, Rawalpindi in partial fulfillment for the requirements of a B.E. Degree in Electrical (Telecommunication) Engineering JUNE 2014

## ABSTRACT

### MOBILE VIDEO SURVEILLANCE

Surveillance systems have been going through an era of development. This has been mainly because of the increasing need of security. Real-time surveillance has gained rising popularity due to their automatic surveillance and security actions. This mobile video surveillance is a real time intelligent system based on FPGA (Field Programmable Gate Array). It provides the functionality of monitoring, security and control in order to improve efficiency of security system with respect to timing constraints. There are two units of the system: the first being FPGA which is connected with motion sensors, IP camera and GPRS/GSM module and the second unit is the mobile phone. Sensors monitor the target area including the entrance as well as windows. The video of the target area is continuously captured by the IP camera. In case of any abnormal situation, alarm messages are sent to the user's mobile through GPRS/GSM module. The video is then transmitted to the user through Wi-Fi module. The user also has the option to arm/disarm the system.

## DECLARATION

No portion of the work presented in this dissertation has been submitted in support of another award or qualification either at this institution or at elsewhere.

Copyright by Zainab Khalid Zunaira Sajjad Samoona Aslam Jovaria Maqsood

## **DEDICATION**

In the name of Allah, the Most Merciful, the Most Beneficent.

To our parents, without whose constant support and unstinting cooperation and assistance a work of this magnitude would not have been possible.

## ACKNOWLEDGEMENTS

All praises for Allah Almighty who gave us the strength to accomplish this mighty task despite numerous difficulties and hardships on our way.

We offer our utmost gratitude to our Supervisor, Lec Intisar Rizwan-i-Haque for his constant guidance and encouragement. He gave us hope and boosted up our confidence during the tough phases of our project. The project wouldn't have been possible without his expert advice, unfailing patience and invaluable efforts.

We are also grateful to our parents and family for their admirable support and last but not the least, our auspicious university for making us what we are today.

# **Table of Contents**

| Chapter                                              | Page no. |

|------------------------------------------------------|----------|

| Chapter 1: Introduction                              | 1        |

| 1.1. Project Overview                                | 1        |

| 1.2. Problem Statement                               | 1        |

| 1.3. Project Scope                                   | 1        |

| 1.4. Objectives                                      | 2        |

| 1.5. Deliverables                                    | 2        |

| 1.6. Conclusion                                      | 2        |

| Chapter 2: Literature Review                         | 3        |

| 2.1. Surveillance                                    |          |

| 2.2. Video Surveillance                              |          |

| 2.3. FPGA                                            | 4        |

| 2.4. Verilog                                         | 5        |

| 2.5. IP Cores                                        | 5        |

| 2.6. Virtex-6 embedded tri-mode Ethernet MAC wrapper | б        |

| 2.7. Conclusion                                      | 6        |

| Chapter 3: Technological Requirements                | 7        |

| 3.1. Hardware Requirements                           |          |

| 3.1.1. Virtex-6 XC6VLX240T-1FFG1156                  |          |

| 3.1.2. SIM900 Module                 |

|--------------------------------------|

| 3.1.3. IP Camera                     |

| 3.1.4. Laptop and Mobile phone       |

| 3.1.5. Wi-Fi Router                  |

| 3.1.6. Switch                        |

| 3.1.7. Motion Sensor                 |

| 3.2. Software Requirements           |

| 3.2.1. Xilinx ISE Design suite       |

| 3.2.2. iSpy                          |

| 3.2.3. IP cam viewer                 |

| 3.2.4. Wireshark                     |

| 3.2.5. Docklight                     |

| 3.3. Conclusion                      |

| Chapter 4: Design and Development 17 |

| 4.1. System Overview                 |

| 4.1.1. System Block Diagram          |

| 4.2. Operating Frequencies           |

| 4.3. Hardware Integration            |

| 4.3.1. Interfacing Motion Sensor     |

| 4.3.2. GSM Module                    |

| 4.3.3. Ethernet                                    |

|----------------------------------------------------|

| 4.4. Video Storage                                 |

| 4.4.1. Camera Settings                             |

| 4.4.2. Video Storage On Detection                  |

| 4.4.3. Assigned Directory                          |

| 4.5. Conclusion                                    |

| Chapter 5: Project Analysis and Evaluation 32      |

| 5.1. Top Module                                    |

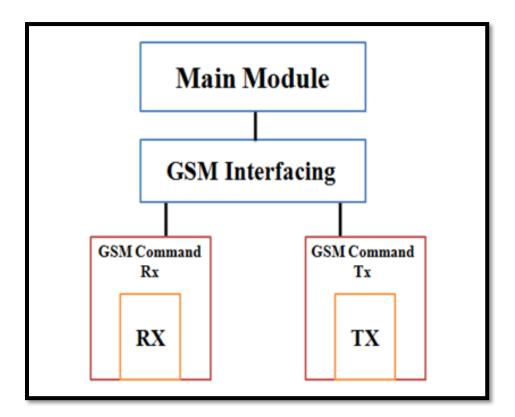

| 5.2. GSM Command Transmitter Module                |

| 5.3. GSM Command Receiver Module                   |

| 5.4. GSM Interfacing Module                        |

| 5.5. Ethernet Core Generation                      |

| 5.5.1. Ethernet Module-Eth 0 (Copper Interface) 40 |

| 5.5.2. SFP Module Eth1 (Optical Interface)         |

| 5.6. Conclusion                                    |

| Chapter 6: Future Work and Conclusion46            |

| 6.1. Future Work                                   |

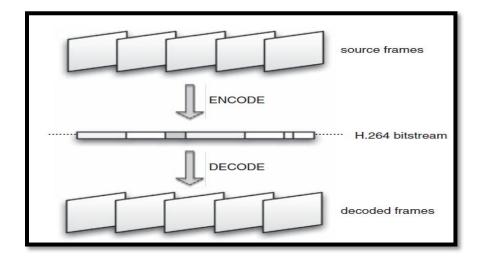

| 6.1.1. H.264 Video Compression                     |

| 6.1.2. Encryption and Decryption of Video          |

| 6.1.3. Face detection and fingerprint algorithms   |

| 6.1.4. Object Classification         |    |

|--------------------------------------|----|

| 6.1.5. Increase in the coverage area |    |

| 6.2. Conclusion                      |    |

| Chapter 7: Bibliography              | 50 |

| APPENDIX A-1                         | 51 |

| APPENDIX A-2                         | 59 |

| APPENDIX A-3                         | 64 |

| APPENDIX A-4                         | 76 |

## LIST OF TABLES

| Table                                                            | Page no. |

|------------------------------------------------------------------|----------|

| Table 3-1: Features of Virtex-6 XC6VLX240T-1FFG1156              | 9        |

| Table 4-1: Operating frequencies                                 |          |

| Table 4-2: Sensor pin assignment on FPGA                         |          |

| Table 4-3: SIM900 module and FPGA interfacing                    |          |

| Table 4-4: Communication between FPGA and user via SIM900 module |          |

| Table 4-5: Number of bits for frame                              |          |

| Table 5-1: Top module design summary                             |          |

## LIST OF FIGURES

| Figure                                              | Page no. |

|-----------------------------------------------------|----------|

| Figure 3-1: Breakdown of technological requirements | 7        |

| Figure 3-2: Block diagram of Virtex-6               |          |

| Figure 3-3: Virtex-6 board                          | 9        |

| Figure 3-4: SIM900 module                           | 11       |

| Figure 3-5: IP camera                               | 11       |

| Figure 3-6: Live video transmission on mobile phone |          |

| Figure 3-7: Motion sensor                           | 13       |

| Figure 4-1: System layout                           |          |

| Figure 4-2: System block diagram                    |          |

| Figure 4-3: GSM module                              |          |

| Figure 4-4: System interfacing                      |          |

| Figure 4-5: FPGA interfacing with FPGA and router   |          |

| Figure 4-6: Frame processing                        |          |

| Figure 4-7: Camera settings                         |          |

| Figure 4-8: Video storage on detection              |          |

| Figure 4-9: Stored clips in software                |          |

| Figure 5-1: Top module                              |          |

| Figure 5-2: Top module design in Xilinx             |          |

| Figure 5-3: GSM command transmitter module          |          |

| Figure 5-4: GSM command receiver module             | 35       |

| Figure 5-5: GSM interfacing module                  |          |

| Figure 5-6: RTL schemeatic of Top module | . 39 |

|------------------------------------------|------|

| Figure 5-7: Ethernet core generation     | . 41 |

| Figure 5-8: BANK33                       | . 42 |

| Figure 5-9: SFP module core generation   | . 43 |

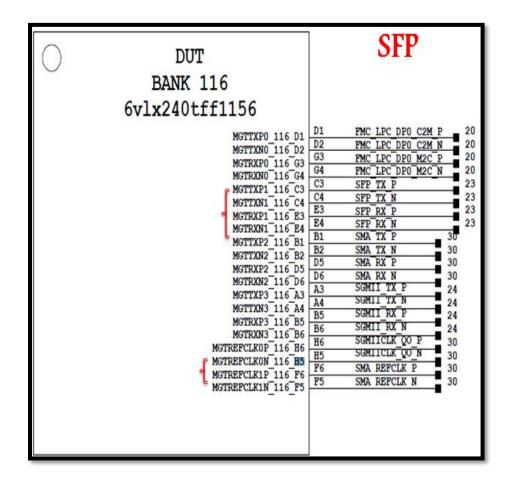

| Figure 5-10: BANK 116                    | . 44 |

| Figure 6-1: Video coding                 | . 47 |

## LIST OF ABBREVIATIONS

| ACE   | Advanced Configuration Environment      |  |

|-------|-----------------------------------------|--|

| AVI   | Audio Video Interleaved                 |  |

| BPI   | Byte Peripheral Interface               |  |

| CF    | Compact Flash                           |  |

| CCTV  | Closed-circuit television               |  |

| CMOS  | Complementary metal-oxide-semiconductor |  |

| CAT 5 | Category 5                              |  |

| DDR3  | Double Data Rate Type Three             |  |

| FPGA  | Field-programmable gate array           |  |

| GPIO  | General-Purpose Input/Output            |  |

| GPRS  | General packet radio service            |  |

| GMII  | Gigabit Media Independent Interface     |  |

| HDL   | Hardware description language           |  |

| I/O   | Input/output                            |  |

| IP    | Internet Protocol                       |  |

| IR    | Infrared                                |  |

| JTAG  | Joint Test Action Group                 |  |

| JPEG  | Joint Photographic Experts Group        |  |

| LED   | Light Emitting Diode                    |  |

| LCD   | Liquid Crystal Display                  |  |

| MAC   | Media Access Control                    |  |

| M2M   | Machine-to-Machine                      |  |

| MJPEG  | Motion Joint Photographic Experts Group     |  |

|--------|---------------------------------------------|--|

| РНҮ    | Physical Layer                              |  |

| PCS    | Physical Coding Sub-Layer                   |  |

| PMA    | Physical Media Access                       |  |

| RGMI   | Reduced Media Independent Interface         |  |

| RTL    | Register Transfer Level                     |  |

| SODIMM | Small Outline Dual In-Line Memory Module    |  |

| SMA    | SubMiniature Version A                      |  |

| SGMII  | Serial Gigabit Media Independent Interface  |  |

| SFP    | Small Form-Factor Pluggable                 |  |

| ТСР    | Transport Control Protocol                  |  |

| USB    | Universal Serial Bus                        |  |

| UART   | Universal Asynchronous Receiver/Transmitter |  |

| UCF    | User Constraint File                        |  |

| VGA    | Video Graphics Array                        |  |

| Wi-Fi  | Wireless Fidelity                           |  |

# Chapter 1: Introduction

This chapter will give a brief description of the design and will explain why there was a need to develop an effective anti-theft system. It will then explain the objectives, scope and deliverables of the project.

## 1.1. Project Overview

This mobile video surveillance system is a real time intelligent system based on FPGA. It provides the functionality of monitoring, security and control with the help of IP camera, motion sensor and GPRS/GSM module.

### **1.2. Problem Statement**

In light of the worsening crime situations, the need for efficient security system has increased. People lead busy lives, come in and out of work, go on vacations, and run errands so they need to access a live view of their security cameras when they are away from their home or business. Thus, most of the time one is not actually able to be on the site where cameras are installed. Therefore, a real time mobile video surveillance system based on FPGA has been designed. One of the primary benefits of this system is that the user can view the target area on his mobile anywhere provided that there is internet access.

### **1.3. Project Scope**

The surveillance system can serve as a handy tool for monitoring indoor environment. The intruder can be detected within a range of 12m.

## **1.4. Objectives**

The objective is to design an efficient security system using FPGA. Due to the increasing threats people want security systems that can warn them instantly and provide them access to the live video of the target area even if they are not on the site (where the camera is installed). The following user requirements form the target objectives of our project:

- Reception of alarm messages on mobile phone in case of an intrusion that detected by motion sensor

- Knowledge of the location through which the intruder has entered

- Access to the video through internet

- Video can be monitored remotely through mobile

- Backup storage

## **1.5. Deliverables**

The end goal is to have an embedded real time interactive video transmission and control system to meet the actual needs for home security, monitoring the target area remotely, and to prevent car-theft.

## 1.6. Conclusion

Mobile video surveillance is an intelligent security system which has the functionality of providing access to the video of the target area remotely to the user.

# Chapter 2: Literature Review

This chapter will include the literature review conducted from the start of the project and will give brief description of the important concepts related to the project.

Throughout the project, literature review was an ongoing process. In order to gain more knowledge and learn the necessary skills required to complete this project, it was very essential to refer to the variety of sources.

#### 2.1. Surveillance

To monitor the activities, changing information and behavior, mostly regarding people is surveillance. Usually government organizations observe a a particular suspected group or individuals.

#### 2.2. Video Surveillance

Over the years, video surveillance has been a well-known security tool since it allows the user to monitor the target area remotely. Due to advancement in technology, security cameras have shown a great deal of improvement. It is a commonly deployed surveillance technique in contrast to the other types of surveillance. Banks, offices, markets and others are highly dependent on these effective surveillance systems.

CCTV (Closed Circuit Television) analog systems were used in the past, they can be expensive because they require constant maintenance. Cost effective, simple to operate and flexibility are some praise worthy features of digital technology. In order to match user's specific needs, Security systems deploying IP (Internet Protocol) cameras are a good option since they are easy to install and maintain.

### **2.3. FPGA**

FPGA stands for "Field Programmable Gate Array". FPGA essentially is a huge array of gates, which can be programmed and reconfigured anytime anywhere. FPGAs are manufactured by companies like Xilinx, Altera, Actel etc. We implemented different tutorials on Spartan-3E regarding VGA, LCD display, instantiation etc initially. [1]

For basic understanding of FPGA some tutorials were implemented using Spartan 3-E Starter Kit. The software used was Xilinx ISE 12.3. Brief description of these tutorials is given below:

- Simple introductory project: This tutorial consisted of two parts. The first was linked to the design of the program and circuit implementation. The second step was the test bench simulation in order to test the project. The results were simulated by giving the inputs and observing the outputs. [2]

- Multiple instantiations of same component: In this tutorial, a single component was created and simulated. Replicating the components three times was another task.

[3]

- **IP cores:** In order to incorporate an IP core into the project, it was learnt how to use Xilinx's CORE Generator System by creating a multiplier. [4]

- Image generation on the Digilent Spartan 3-E board: In this tutorial, images were generated on the VGA (Video Graphics Array) monitors by implementing a VGA

controller. An encryption algorithm was written to show this implementation. To display the video on the screen of the monitor, VGA display port was used. [5]

• Serial RS-232: RS-232 port was used control the frequency of a simple 4-bit counter using hyperterminal in which five different frequencies were used. A laptop was connected with an FPGA kit using available RS-232 port on the board. [6]

### 2.4. Verilog

The hardware designers in industry and academia use Verilog as one of the major Hardware Description Languages (HDL). The second one being VHDL. It is easier to learn Verilog as compared to VHDL. Verilog HDL uses four different levels of abstraction including architectural or behavioral level as well as gate and switch levels. Three important levels of abstractions are as follows:

- **Behavioral Level**: Concurrent algorithms are used to describe this level. There are a set of instructions which are executed sequentially. Main elements include functions, tasks and always block.

- **Register-Transfer Level:** Transfer of data between the registers and characteristics of circuits by operations are specified by register transfer level.

- Gate Level: Logical links and timing properties describe the characteristics of the system. Discrete Signals can have definite logic values. [7]

### 2.5. IP Cores

Xilinx Targeted Design Platforms key building blocks consist of Intellectual Property (IP) cores. To easily create Plug-and-Play IP, Xilinx FPGA tools and designs play an important role. The market and general specific needs of the end users can easily be met with the help of an extensive catalog of cores. This provides with a competitive advantage. [8]

## 2.6. Virtex-6 embedded tri-mode Ethernet MAC wrapper

For the generation of HDL wrapper files for the Ethernet core in Virtex-6, the CORE Generator Virtex-6 Embedded Tri-mode Ethernet Media Access Controller (MAC) Wrapper is used. Depending on the user requirements, simulation scripts, HDL wrappers and test benches are generated automatically through core generation functionality of Xilinx ISE. Its striking features include:

- A physical interface that is user configurable

- The connection between the PHY and Ethernet MAC is simplified

- SGMII or 1000base-X interfaces with single bit stream

- 2.5 Gbps as the upper limit for 1000base-X interface

- In GMII/MII or RGMII modes, Clock Enable inputs are available

#### 2.7. Conclusion

The literature review carried out was mainly focused on the tutorials performed on Spartan-3E starter kit, learning Verilog, features of Virtex-6 and learning about various components used in the project for e.g. IP camera, motion sensors etc.

# **Chapter 3: Technological Requirements**

This chapter will provide a brief overview of the technological requirements for the project "Mobile video surveillance".

Mobile Video Surveillance provides three functionalities i.e. monitoring, security and control. For monitoring purposes, an IP camera is required to be interfaced with FPGA kit. A Wi-Fi router is required so that the captured video can be viewed anywhere on the mobile phone provided that there is internet access.

For storage purposes, a backup is required which can save the video clip whenever an intruder is detected so that incase the user didn't view the message or was unable to view the video, he can still view the video clip later through backup.

The technological requirements are sub-divided into hardware and software and are discussed in the following sub-sections. Figure 3-1 shows valid breakdown of Technological Requirements.

Figure 3-1: Break down of technological requirements

## **3.1. Hardware Requirements**

The Hardware required for the implementation of the project includes:

### 3.1.1. Virtex-6 XC6VLX240T-1FFG1156

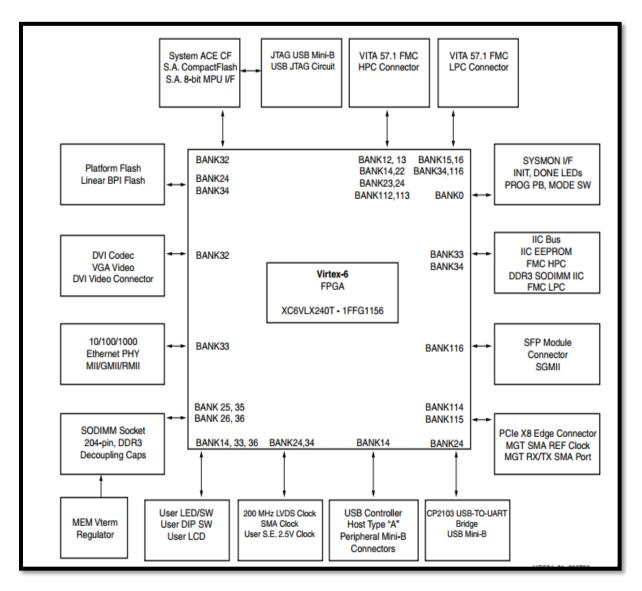

Virtex-6 board was selected because two Ethernet ports were required for the project. As it can be seen in Figure 3-3 that virtex-6 comprises of both these ports.

Figure 3-2: Block diagram of Virtex-6

Figure 3-3: Virtex-6 board

Few important features of this board are discussed in Table 3-1.

| No. | Feature                       | Notes                          |

|-----|-------------------------------|--------------------------------|

| 1   | FPGA Virtex-6                 | XC6VLX240T-1FFG1156            |

| 2   | DDR3 SODIMM                   | Micron 512 MB MT4JSF6464HY-1G1 |

| 3   | 128 MB Platform Flash         | Xilinx XCF128X-FTG64C          |

| 4   | Linear BPI Flash              | Numonyx JS28F256P30T95         |

| 5   | System ACE CF Controller      | Xilinx XCCACE-TQ1441           |

|     |                               | (bottom of board)              |

| 6   | JTAG Cable Connector (        | USB JTAG circuit               |

|     | USB Mini-B)                   |                                |

|     | Clock generation              | 200 MHz OSC, SMA connectors    |

|     | a. 200 MHz oscillator (on     | siTime 200 MHz 2.5V LVDS OSC   |

|     | backside)                     |                                |

| 7   | b. oscillator socket, single- | MMD Components 66 MHz 2.5 V    |

|     | ended                         |                                |

|     | c. SMA connectors             | SMA pair                       |

|    | d. MGT REFCLK SMA            | SMA pair                                 |

|----|------------------------------|------------------------------------------|

|    | connectors                   |                                          |

| 8  | SFP connector                | AMP 136073-1                             |

| 9  | Ethernet (10/100/1000) with  | Marvel M88E1111 EPHY                     |

|    | SGMII                        |                                          |

| 10 | USB Mini-B, USB-to-UART      | Silicon Labs CP2103GM bridge             |

| 11 | USB-A Host, USB Mini-B       | Cypress CY7C67300-100AXI                 |

|    | peripheral connectors        |                                          |

| 12 | Video- DVI connector         | Chrontel CH7301C-TF codec                |

|    | Status LEDs                  |                                          |

| 13 | a. Ethernet status           | Right-angle link rate and direction LEDs |

|    | b. FPGA INIT, DONE           | Init (red), done (green)                 |

|    | c. system ACECF status       | Status (green), Error (red)              |

|    | User I/O                     |                                          |

|    | a. User LEDs, green(8)       | User I/O (active-High)                   |

|    | b. User pushbuttons, N.O.    | User I/O (active-High)                   |

|    | momentary (5)                |                                          |

| 14 | c. User LEDs, green (5)      | User I/O (active-High)                   |

|    | d. User DIP switch (8-pole)  | User I/O (active-High)                   |

|    | e. User GPIO SMA             | SMA pair                                 |

|    | connectors                   |                                          |

|    | f. LCD 16 Character x 2 line | Displaytech S162D BA BC                  |

|    | display                      |                                          |

|    | Switches                     |                                          |

|    | a. Power ON/OFF              | Slide switch                             |

|    | b. FPGA –PROG- B Push        | Active-low                               |

| 15 | button                       |                                          |

#### 3.1.2. SIM900 Module

SIM900 Module works on a number of frequencies including 850 MHz, 900 MHz, 1800 MHz and 1900 MHz. To use as plug in GSM modem is really easy to use and portable. The PC Serial port can be directly connected with the RS232 Level converter on the modem. The AT commands can be used to configure the baud rate where by initially it is in Auto baud mode. To enable the user to connect with internet via GPRS, the GSM/GPRS RS232 modem has an internal TCP/IP stack. It can be used for data transfer as well as SMS applications.

Figure 3-4: SIM900 module

#### 3.1.3. IP Camera

IP camera used provides Day/Night high-resolution image. The Compression format used is Motion-JPEG. Its resolution is CMOS 300,000 pixels. Pan Horizontal rotation is 0-270° whereas tilt vertical rotation is 0-90°. Its range is up to 10m. Multiple users can access it at the same time and it can be protected with the help of a password.

Figure 3-5: IP camera

### 3.1.4. Laptop and Mobile phone

Laptops are required to create backup storage. In case the user doesn't has internet access and is unable to receive live transmission of video, he still can watch the video clip later through backup storage. Mobile phone is required to view the video captured by the IP camera.

Figure 3-6: Live video transmission on mobile phone

### 3.1.5. Wi-Fi Router

Wi-Fi router is needed to assist wireless video transmission on mobile phone. The user can monitor his home even when he is far away.

## 3.1.6. Switch

The TP-LINK with 5 ports can be used as a switch to covert to Gigabit Ethernet.

### **3.1.6.1.** Features

- Five 10/100/1000Mbps RJ-45 port

- Auto-Negotiation, Auto MDI/MDIX, Half/Full duplex

- IEEE 802.3 flow control

- Plug and play

- 15K jumbo frame

## 3.1.7. Motion Sensor

Motion sensors are deployed at multiple locations like windows, doors etc. on a single site. The model required for the project is HVR-SA 1200. It can easily detect movement

within an area of 40 feet with a detection angle of 180°. Its sensitivity can be increased and decreased according to the requirements of the user. Day/night settings can also be adjusted.

Figure 3-7: Motion sensor

## **3.2. Software Requirements**

The software(s) required for the implementation of the project includes:

### 3.2.1. Xilinx ISE Design suite

Xilinx ISE 13.4 was used for the coding of the design. Xilinx has produced Xilinx ISE (Integrated Software Environment) software tool that is used for synthesis and analysis of HDL designs that enables the developer the following:

- The design can be synthesized

- Timing analysis can be performed

- Register-transfer level diagrams examination

- A design's reaction to different stimuli can be simulated

• The programmer can configure the target device

#### 3.2.2. iSpy

The libraries and programs needed for handling multimedia data are provided by iSpy connect which is open source software. To detect and record movement or sound and provides features of monitoring, alerting, surveillance, and security, iSpy uses webcams and microphones. All the captured media is made available securely over the web. It can be run on many computers together [9]. Following are the functions that it performs:

- When motion is detected it automatically captures images

- Motion detection trigger level that is adjustable

- 99 cameras can be supported

- Capability of DVR card

- Capability of multiplexing

- Sensitivity level of image can be adjusted

- Image Archiving (1,000s of images)

#### 3.2.3. IP cam viewer

Real time video from IP or USB cameras can be viewed on mobile phone by using IP Camera Viewer. Wherever security is required, any USB or IP camera can be used, be it your home, office or parking area.

Up to 4 camera feeds can be controlled by the user simultaneously. By using this lightweight application, the user can get a live preview from multiple cameras. By using

centralized camera and layout management, the user can view cameras from multiple remote locations on a single screen. To cater the security needs, the user can change the arrangement and preview layout of the cameras. [10]

The orientation of camera preview can also be adjusted. By supporting many PTZ (Pan/Tilt/Zoom) enabled network cameras, it helps in adjusting the coverage area. IP Camera Viewer provides an additional functionality of digital zoom irrespective of the fact whether it is supported or not.

#### 3.2.4. Wireshark

This software is an open-source and free packet analyzer. Analysis, communications protocol development, network trouble shooting are some of its features [11].

It understands the encapsulation procedure of different networking protocols. Together with the meanings, it can display the fields and parse as specified by different networking protocols. Following are the features of Wireshark:

- Hundreds of protocols can be inspected

- Can perform offline analysis and live capture

- Three-pane packet browser as the standard

- A Multi-platform software supported on Linux, Windows, Solaris, OS X, netbsd, and FreeBSD

- Display filters that are the most powerful

- Rich VoIP analysis

- Captured gzip compressed files can be decompressed on the fly

Allows live data reading from IEEE 802.11, PPP/HDLC, Ethernet, Bluetooth, ATM, Ring, Frame Relay, Token, USB and FDDI

## 3.2.5. Docklight

For serial communication protocol, Docklight is an analysis, simulation and testing tool. It can be used for testing the serial communication of a single device and for monitoring the communication between two serial devices. Communications automotive, automation and control, consumer products and equipment manufacturers are some industry areas where productivity can be increased using Docklight. Lastly it is very easy to use.[12]

## **3.3.** Conclusion

The hardware part of the project consists of Virtex-6 kit, SIM900 module, IP camera, motion sensors, switches and router. Xilinx Design Suite 13.4, Docklight, Wireshark and IP cam Viewer are the softwares that were used to carry out different tests.

# Chapter 4: Design and Development

This chapter will provide information regarding the methodology and approach leading to the development of this project.

#### **4.1. System Overview**

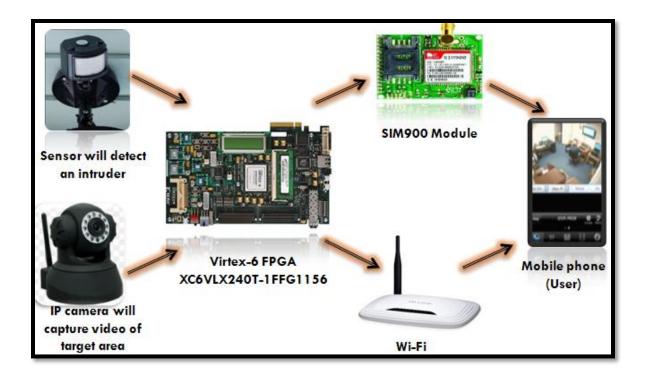

There are two units of the system: the first being FPGA which is connected with the sensors and IP camera along with the SIM900 module and the second unit consists of mobile phone. Target area will be monitored by sensors installed at certain locations including the entrance as well as the windows. The video of the target area will be continuously captured by the rotatable IP camera that is connected to the Ethernet port of FPGA via switch. When an intruder will enter, the system will send 'INT AT LOC X' (Intruder at location x) message to the mobile user via SIM900. The user can than view the video of the target area in his mobile phone by providing the correct username and password. In a highly secure place, the number of police station can also be added so in case an intruder enters, the message will be sent to them as well. If the user fails to read the message at that time, the user can view the video later that will be stored using video storage software. The user can also ARM/DISRAM the system. When the user wants to stop the system, he will send a 'DIS' (Disarm) message to FPGA via SIM900.

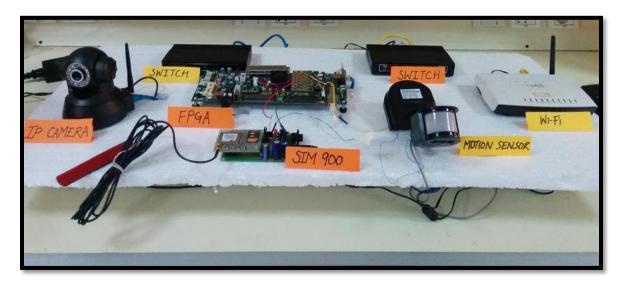

Figure 4-1: System layout

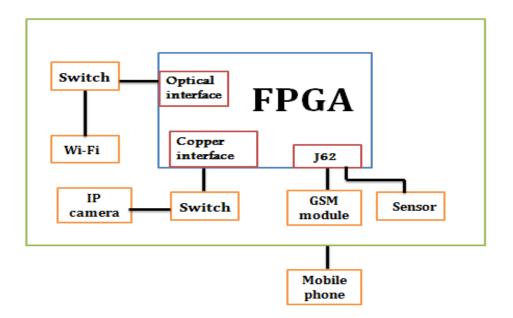

#### 4.1.1. System Block Diagram

Figure 4-2 shows the system block diagram of Mobile Video Surveillance. The sensor is connected to the FPGA through J62 pins and IP camera is connected to the Ethernet port on FPGA. The SIM900 GPRS/GSM module is also connected to the FPGA kit through J62 pins which acts as the communication medium between the FPGA and the mobile station. By using this unit, information is sent from the FPGA to the mobile station and the instructions are sent from the mobile station to the FPGA. FPGA executes any instruction sent by the user from the mobile station. Any mobile phone that can send and receive messages can be used for this purpose. The instructions that are sent to FPGA and any alert from the FPGA is received in form of a message. The video that is captured through the IP camera is transmitted through Wi-Fi. Wi-Fi device is connected to the switch which is further connected to the SFP port on FPGA.

Figure 4-2: System block diagram

## 4.2. Operating Frequencies

Table 4-1 gives the operating frequencies of various modules of the system.

| Table 4-1: Operating | frequencies |

|----------------------|-------------|

|----------------------|-------------|

| Module                   |               | Operating Frequency |  |

|--------------------------|---------------|---------------------|--|

| Eth 1 (optic             | al interface) | 125 MHz             |  |

| Eth 0 (copper interface) |               | 125 MHz             |  |

| GSM                      | Тх            | 1200 Hz             |  |

|                          | Rx            | 16 x 1200 Hz        |  |

## 4.3. Hardware Integration

The hardware development of Mobile Video Surveillance revolves around Virtex-6 XC6VLX240T-1FFG1156 FPGA. All the modules including motion sensor, SIM900 and IP camera are interfaced with Virtex-6 XC6VLX240T-1FFG1156 FPGA.

#### 4.3.1. Interfacing Motion Sensor

Sensors will be installed at various locations in the target area. When an intruder will enter, the signal will be cut and a message "INT AT LOC X" will be sent from FPGA to the user via SIM900 module. Motion sensors are assigned on the dip switches on FPGA. Their assignment is shown in Table 4-2

| U1 FPGA Pir | Schematic Net | Pin            | Function assigned  |

|-------------|---------------|----------------|--------------------|

| L20         | GPIO_DIP_SW   | DIP Switch Pin | Sensor at location |

|             | 4             | SW1.4          | 1                  |

| L21         | GPIO_DIP_SW   | DIP Switch Pin | Sensor at location |

|             | 3             | SW1.3          | 2                  |

Table 4-2: Sensor pin assignment on FPGA

Schematic Net name is used to search the general purpose input output Dip switch FPGA pin on the schematics. U1 FPGA pin number is used in the UCF (User Constraint File). FPGA pin L20 and L21 are assigned the functionality of sensor at location 1 and location 2. When the Dip switch 4/3 is high indicating that the signal is cut, a message that an intruder has entered from location 1/2 is sent to the user.

#### 4.3.2. GSM Module

GSM command transmitter module is used to send messages. The five commands that are Test connect, Set number, Set text, Send message and Delete all messages are executed sequentially. GSM command receiver module is used to receive messages. The messages that are received by the system are ARM and DISARM. GSM command transmitter and receiver together comprise the GSM interfacing module which is part of the Top module in FPGA design. The top module also includes the Ethernet module and the SFP module.

Figure 4-3: GSM module

## 4.3.2.1. Interfacing SIM900 module

Figure 4-4: System interfacing

J62 pins of FPGA are used to interface SIM900 module with FPGA. The connections are explained in Table 4-3.

| U1 FPGAPin | Schematic Net<br>Name | Pin                               | Controlled LED | Function<br>assigned  |

|------------|-----------------------|-----------------------------------|----------------|-----------------------|

| D22        | GPIO_DIP_SW1          | DIP Switch Pin<br>SW1.1           | _              | SIM900 enable         |

| G26        | GPIO_SW_C             | Pushbutton<br>Switch Pin<br>SW9.2 | _              | Reset                 |

| AC22       | GPIO_LED_0            | GPIO J62 Pin 1                    | D\$12          | SIM900<br>Receiver    |

| AD24       | GPIO_LED_7            | GPIO J62 Pin 8                    | D\$21          | SIM900<br>Transmitter |

The pin D22 is assigned the functionality of enabling SIM900 module. G26 pin resets the system. A wire from pin AC22 (FPGA transmitter) is connected to SIM900 receiver slot. It performs the functionality of transmitting the messages from FPGA to the user. A wire from AD24 (FPGA receiver) is connected to SIM900 transmitter slot. It performs the functionality of receiving the messages from the user to the FPGA.

#### 4.3.2.2. Communication between FPGA and User via SIM900 Module

The SIM900 GPRS/GSM module acts as the communication medium between the FPGA and the mobile station. By using this unit, information is sent from the FPGA to the mobile station and the instructions are sent from the mobile station to the FPGA. This communication is done in form of text messages.

| Action          | Message transmitted | Transmitter | Receiver |

|-----------------|---------------------|-------------|----------|

| System powers   | "POWER"             | FPGA        | User     |

| ON              |                     |             |          |

| When the signal | "INT AT LOC X"      | FPGA        | User     |

| is cut (sensor) |                     |             |          |

| To disable      | "DIS"               | User        | FPGA     |

| transmission of | 215                 | 0501        | man      |

| video           |                     |             |          |

| To enable       | "ARM"               | User        | FPGA     |

| transmission of | ANN                 | 0361        | non      |

| video           |                     |             |          |

Table 4-4: Communication between FPGA and user via SIM900 module

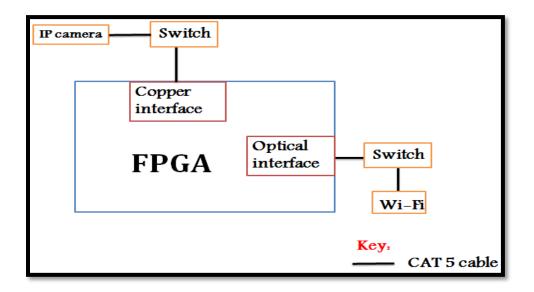

## 4.3.3. Ethernet

IP Camera is used to capture the video of the target area which is connected to Copper interface (Eth 0) of FPGA via switch. The IP camera operates on 100 Mbps. The Copper

interface of FPGA can work on 10/100/1000Mbps but due to its complexity, 1000Mbps have been used, so there was a need to use a switch between the camera and copper interface. A camera with Gbps interface could also be used but due to it's unavailability it was not used. The switch performs auto-negotiation (converts from Mbps (IP camera) to Gbps (FPGA)). This video is then transmitted from optical interface of FPGA to the user via switch.

Figure 4-5: FPGA interfacing with FPGA and router

The following ports will be physically connected through CAT 5 cable with RJ-45 connectors at both the ends.

- IP camera and switch

- Switch and Eth 0 (Copper interface FPGA)

- Eth 1 (Optical interface FPGA) and switch

- Switch and router

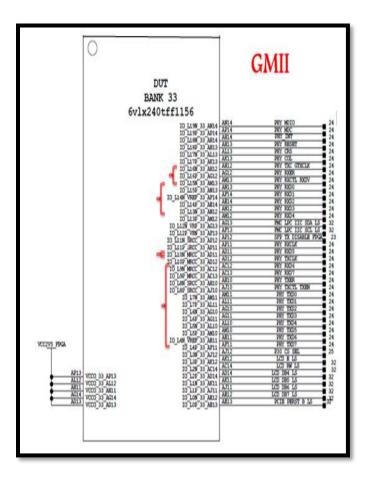

#### **4.3.3.1.** Ethernet Core Design and Configuration

Xilinx's Core Generator tool was used to design a Virtex-6 Embedded Tri-mode Ethernet MAC Wrapper to enable the Ethernet ports of FPGA board. The wrapper that we designed through the software was for standard Virtex-6 FPGA board (ML605), therefore it had to be configured according to the FPGA board available, i.e. Virtex 6 (xc6vlx240t, ff1156) to enable its Ethernet ports. Therefore the entire UCF of the project was changed according to the development board. The changes that were made are shown in the Figure 5-6 and 5-8.

Changing the UCF was quite a challenging task. BANK33 and BANK116 were used from schematics of Virtex-6 (ML605) inorder to change the UCF. The following options for the interfaces were used during the core generation in Xilinx ISE 13.4.

#### **Eth0** (copper interface):

- Virtex-6 Tri-Mode Ethernet MAC Wrapper 1.5

- PHY interface: GMII

- BANK 33

#### **Eth1 (Optical interface):**

- Virtex-6 Tri-Mode Ethernet MAC Wrapper 2.2

- PHY interface: 1000BASE X PCS PMA

- BANK 116

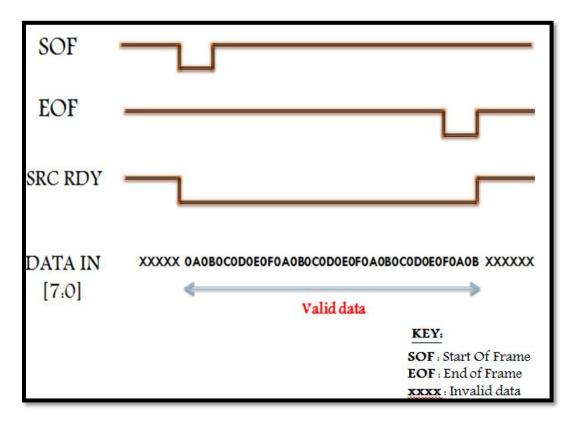

4.3.3.2. Frame Processing

Figure 4-6: Frame processing

At the SOF (start of the frame), as shown in the Figure 4-6, the signal gets low for one cycle. As soon as that happens, the src ready signal also gets low and the reception of valid data starts. 'xxxx' indicates invalid data. The data received during the time the source ready signal is low is the valid data. As soon as the signal gets high during one clock cycle, the src ready signals gets high and it indicates that this is the end of frame. Valid data is recieved for a number of cycles and starts when the frame starts and ends when the frame ends.

The bits utilized by each signal are shown in Table 4-5.

| SIGNALS                | BITS |

|------------------------|------|

| SOF (Start of frame)   | 1    |

| EOF (End of frame)     | 1    |

| SRC RDY (Source Ready) | 1    |

| DATA IN (Data Input)   | 8    |

Table 4-5: Number of bits for frame

### 4.4. Video Storage

Being expensive, closed source, lacking a number of features, restricted data usage, poor control over sensitivity and poor audio control are a number of problems that are linked with the current security and surveillance software. Using iSpy you can do pretty much anything, protecting your business and home with an open source software. iSpy is sensitive to movement and sound so it makes an awesome camera security system. Cameras and microphones can be added, configured and monitored- displaying live video and audio from a variety of network sources. You can switch cameras and microphones on or off, trigger recordings, switch on alerts etc. Following are some important features of iSpy:

- When motion is detected it automatically captures images

- Motion detection trigger level that is adjustable

- 99 cameras can be supported

- Capability of DVR card

- Capability of multiplexing

- Sensitivity level of image can be adjusted

- Image Archiving (1000s of images)

In the project, whenever an intruder enters, motion detector which is installed at entrances detects an intruder and sends alarming messages to user with details of the particular location through which the intruder has entered. The user can then view the live video of the target area in his mobile phone. In case the user fails to view the video at that particular time due to some reasons, he can view the video later which is stored using the iSpy software.

The video storage works on 'Record on detect' i.e. whenever some movement is detected, it starts to record the video and it keeps on recording the video until there is no movement. It will record up to 8 seconds after no movement is detected. The duration for which the video is recorded after no movement is detected can be set according to the user's requirement. After that it will stop recording automatically. These settings are done in order to increase the efficiency since there is no use of continuous storage. It is just wastage of space. The video that is recorded is automatically stored in a local directory as per the user's choice.

Initially cameras are added to the software and camera settings are made according to the camera model and user requirement.

### 4.4.1. Camera Settings

In the camera settings, following settings need to be changed:

- Motion detection: Motion detection sensitivity, display style and number of frames processed can be changed

- Alerts: The alert can be enabled on movement or no movement. The alert interval and the action performed upon alert can be set.

- **Recording:** The recording mode whether to detect on movement or without movement and inactivity recording duration can be set.

- **Storage:** By using this option, the user can set the storage directory and the video storage folder size.

| Talk         |             |          |          |

|--------------|-------------|----------|----------|

| Camera Model | None        | •        | Settings |

| IP Address   | 192.168.1.2 | Port     | 81       |

| Usemame      | admin       | Password |          |

|              |             |          |          |

Figure 4-7: Camera settings

### 4.4.2. Video Storage On Detection

When movement is detected, iSpy starts recording the video. Blue rectangles start appearing around the border of any object that is detected. Under no movement condition, no video is recorded.

Figure 4-8: Video storage on detection

The blue boxes in Figure 4-8 shows that it has detected an intruder as explained above and red dot on top right shows recording has started.

## 4.4.3. Assigned Directory

The recorded clips are stored in the local user assigned directory.

Figure 4-9: Stored clips in software

# 4.5. Conclusion

The hardware integration comprises of interfacing SIM900 module, IP camera and motion sensor with FPGA. Video storage has been done using iSpy which is mainly the backup storage.

# Chapter 5: Project Analysis and Evaluation

In this chapter, simulations will be discussed that were used to evaluate the performance of the project design.

## 5.1. Top Module

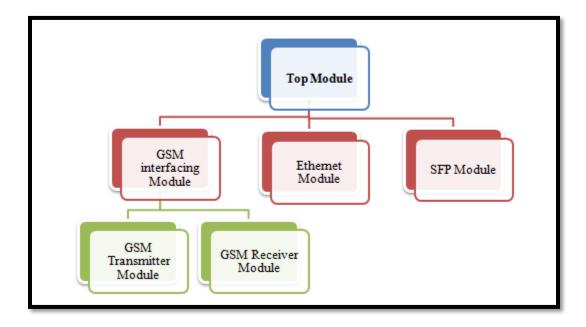

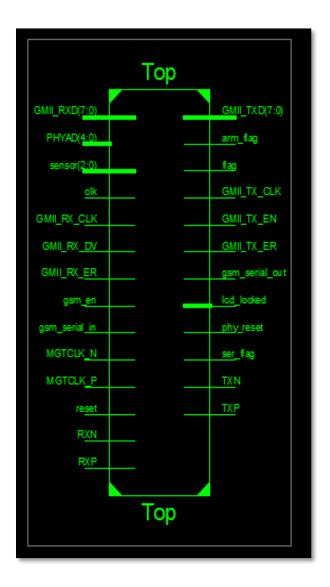

The top module of the project is composed of three sub modules as shown in Figure 5-1.

Figure 5-1: Top module

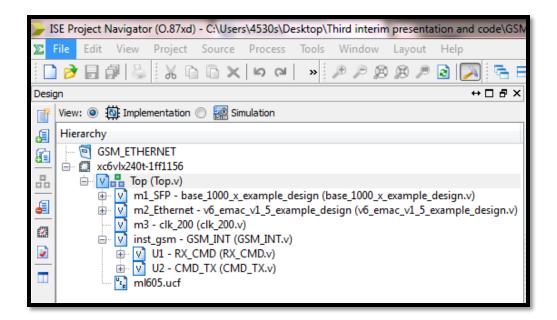

Figure 5-2 shows the design of Top module in Xilinx. The algorithm designed for the project was synthesized, implemented and then its programming file was generated using Xilinx's Project Navigator.

Figure 5-2: Top module design in Xilinx

In order to check whether the designed algorithm was valid or not, initially a test bench was created. Inputs for the test bench were defined within the code. The simulator used was Xilinx's simulator version13.4, IS im.

## 5.2. GSM Command Transmitter Module

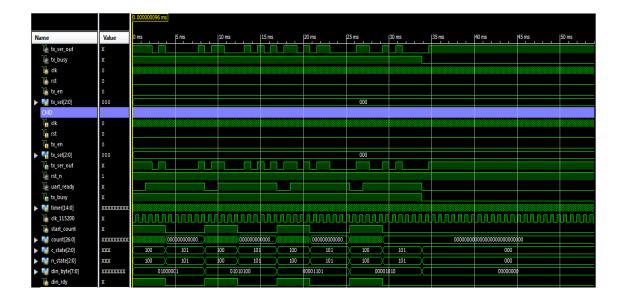

Figure 5-3: GSM command transmitter module

Figure 5-3 shows the timing diagram of GSM command transmitter module. The input of this module is a go\_signal that indicates the system is ready to start and commands can be executed one by one which is received from the main module. If the state of this signal is 0 then it stays at its initial position but if the state is 1 then the signal passes through the selection function. It can be seen in Figure 5-3 that at the positive edge of din\_rdy i.e when the data is ready to be transmitted, eight bits of din\_byte are transmitted during one cycle. The data is stored in the buffer and most significant eight bits of the data are transmitted during one cycle. When all the data has been transmitted, the din\_rdy signal becomes low indicating that there is no data to be transmitted. c\_state and n\_state indicates the current state and the next state of the state machine respectively. There are five different commands that are executed sequentially following the same procedure.

- **Test connect**: This command makes sure that GSM module is connected to the system.

- Set number: This command sets the number of the mobile user with whom the communication is done to control the system.

- Message: This command sets the message that has to be sent.

- Send message: This command sends the text to the user to let him know about the state of the system.

- Delete all messages: This command deletes all the previous inbox messages.

## **5.3. GSM Command Receiver Module**

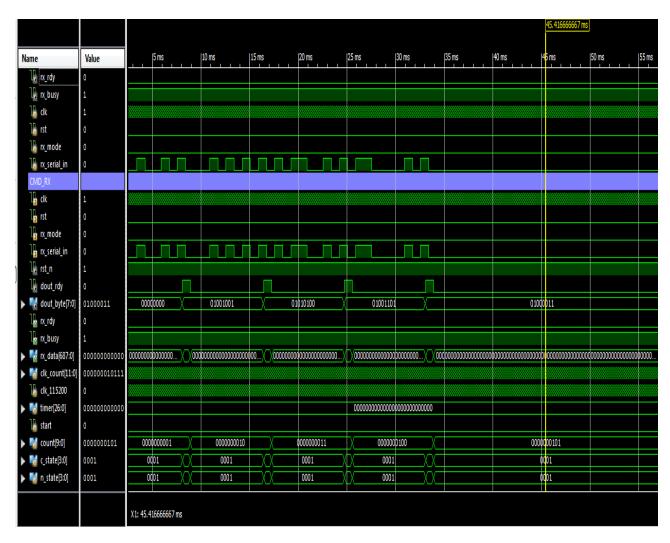

Figure 5-4: GSM command receiver module

This module processes the signal received from the SIM900 module. When message is received, it is checked whether the message is valid or not. Receiver mode can have two states. If receive mode equals 1, the message is valid and if it is equal to 0 then the message is not valid. In above case it is an invalid message i.e. it is an update message for the SIM and rx\_mode is 0, it waits for a particular duration to completely process the update info and waits for dout\_rdy to be 1 (indicates that the o/p is ready to be saved in the next stage) otherwise if 0 then receiving of update info continues as can be seen in

simulation. Four message bytes are meant to be received (the simulation shows that four bytes are received) and if they are valid it goes to output. Now in the other case if the output is valid it goes to other stage of the rx\_mode and waits until all the 86 bytes (688 bits) of message have been received. Waiting is done to receive 86 bytes and then this data is saved in the next stage and further processing is done according to the received command.

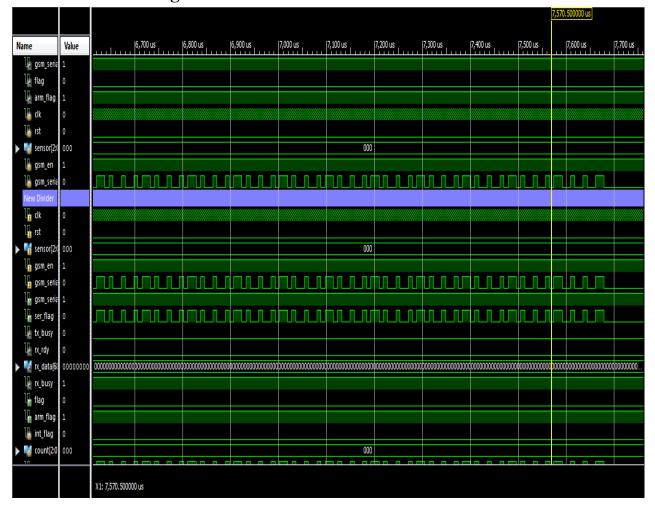

## **5.4. GSM Interfacing Module**

|                                         |               |                                         |                                         |                                         |                                         |                                         |                                         |                                                     |                                         |                                         |                                         |                                                                                                                | 500000 us                               |        |

|-----------------------------------------|---------------|-----------------------------------------|-----------------------------------------|-----------------------------------------|-----------------------------------------|-----------------------------------------|-----------------------------------------|-----------------------------------------------------|-----------------------------------------|-----------------------------------------|-----------------------------------------|----------------------------------------------------------------------------------------------------------------|-----------------------------------------|--------|

| e                                       | Value         |                                         | 6,700 us                                | 6,800 us                                | 6,900 us                                | 7,000 us                                | 7, 100 us                               | 7,200 us                                            | 7,300 us                                | 7,400 us                                | 7,500 us                                | ,                                                                                                              | 7,600 us                                | 7,700  |

| int_flag                                | 0             |                                         |                                         |                                         |                                         |                                         |                                         |                                                     |                                         |                                         |                                         |                                                                                                                |                                         |        |

|                                         | 000           |                                         |                                         |                                         |                                         |                                         | 000                                     |                                                     |                                         |                                         |                                         |                                                                                                                |                                         |        |

| gsm_seria                               |               |                                         |                                         |                                         |                                         |                                         |                                         |                                                     |                                         |                                         |                                         |                                                                                                                |                                         |        |

| -                                       | 0             |                                         |                                         |                                         |                                         |                                         |                                         |                                                     |                                         |                                         |                                         |                                                                                                                |                                         |        |

| -                                       |               |                                         |                                         |                                         |                                         |                                         | 000                                     |                                                     |                                         |                                         |                                         |                                                                                                                |                                         |        |

| -                                       | 0             |                                         |                                         |                                         |                                         |                                         |                                         |                                                     |                                         |                                         |                                         |                                                                                                                |                                         |        |

| rx_en                                   | 0             |                                         |                                         |                                         |                                         |                                         |                                         |                                                     |                                         |                                         |                                         |                                                                                                                |                                         |        |

| timer[26:C                              | 00000000      |                                         |                                         |                                         |                                         |                                         |                                         |                                                     |                                         |                                         |                                         |                                                                                                                |                                         |        |

| start                                   | 1             |                                         |                                         |                                         |                                         |                                         |                                         | ******                                              |                                         |                                         |                                         |                                                                                                                |                                         |        |

| ostate[3:                               |               |                                         |                                         |                                         |                                         |                                         | 000                                     | 1                                                   |                                         |                                         |                                         |                                                                                                                |                                         |        |

|                                         | 0001          |                                         |                                         |                                         |                                         |                                         | 000                                     |                                                     |                                         |                                         |                                         |                                                                                                                |                                         | +      |

| ew Divider                              | 0001          |                                         |                                         |                                         |                                         |                                         | 000                                     |                                                     |                                         |                                         |                                         |                                                                                                                |                                         |        |

| -                                       | 0             |                                         |                                         |                                         |                                         |                                         |                                         |                                                     |                                         |                                         |                                         |                                                                                                                |                                         |        |

|                                         | 1             |                                         |                                         |                                         |                                         |                                         |                                         |                                                     |                                         |                                         |                                         |                                                                                                                |                                         | -      |

| rx_data[6{                              | _<br>00000000 | 000000000000000000000000000000000000000 | 000000000000000000000000000000000000000 | 000000000000000000000000000000000000000 | 000000000000000000000000000000000000000 | 000000000000000000000000000000000000000 | 000000000000000000000000000000000000000 | 000000000000000000000000000000000000000             | 000000000000000000000000000000000000000 | 000000000000000000000000000000000000000 | 000000000000000000000000000000000000000 | 00000                                                                                                          | 000000000000000000000000000000000000000 | 000000 |

| rx_serial_i                             |               | 000000000000000000000000000000000000000 |                                         |                                         | ,00000000000000000000000000000000000000 |                                         |                                         |                                                     | 000000000000000000000000000000000000000 |                                         | 000000000000000000000000000000000000000 | 00000                                                                                                          | 000000000000000000000000000000000000000 | 000000 |

|                                         |               | ******                                  |                                         |                                         |                                         |                                         |                                         |                                                     |                                         |                                         |                                         |                                                                                                                |                                         |        |

| <u> </u>                                |               |                                         |                                         |                                         |                                         |                                         |                                         |                                                     |                                         |                                         |                                         |                                                                                                                |                                         |        |

| ock_11520                               |               |                                         |                                         |                                         |                                         |                                         |                                         |                                                     |                                         |                                         |                                         |                                                                                                                |                                         |        |

|                                         | 00000000      |                                         |                                         |                                         |                                         |                                         | 000000000000000000000000000000000000000 | 00000000000                                         |                                         |                                         |                                         |                                                                                                                |                                         |        |

| 22<br>                                  | 0             |                                         |                                         |                                         |                                         |                                         |                                         |                                                     |                                         |                                         |                                         |                                                                                                                |                                         |        |

| ·                                       | 00000000      |                                         |                                         |                                         |                                         |                                         | 000000                                  |                                                     |                                         |                                         |                                         |                                                                                                                |                                         |        |

|                                         | 0001          |                                         |                                         |                                         |                                         |                                         | 000                                     |                                                     |                                         |                                         |                                         |                                                                                                                |                                         |        |

| · · ·                                   | 0001          |                                         |                                         |                                         |                                         |                                         | 000                                     | 1                                                   |                                         |                                         |                                         |                                                                                                                |                                         |        |

| ew Divider                              |               |                                         |                                         |                                         |                                         |                                         |                                         |                                                     |                                         |                                         |                                         |                                                                                                                |                                         |        |

|                                         |               | V4 7 570 50000                          |                                         |                                         |                                         |                                         |                                         |                                                     |                                         |                                         |                                         |                                                                                                                |                                         |        |

| timer[14:0                              | 01001011      | X1: 7,570.50000                         | U US                                    | ******                                  | *                                       | 4                                       | *******                                 | *****                                               |                                         | *****                                   | 4                                       | k and the second se |                                         |        |

| clk_11520                               |               |                                         |                                         |                                         |                                         |                                         |                                         |                                                     |                                         |                                         |                                         | 00000000                                                                                                       |                                         | ****** |

| start_cou                               |               |                                         |                                         |                                         |                                         |                                         |                                         |                                                     |                                         |                                         |                                         |                                                                                                                |                                         |        |

| count[26:                               |               |                                         |                                         |                                         |                                         |                                         | 000000000000000000000000000000000000000 | d00000000000                                        |                                         |                                         |                                         |                                                                                                                |                                         |        |

| c_state[2:                              |               |                                         |                                         |                                         |                                         |                                         | 000                                     |                                                     |                                         |                                         |                                         |                                                                                                                |                                         |        |

| n_state[2:                              | 000           |                                         |                                         |                                         |                                         |                                         | 000                                     |                                                     |                                         |                                         |                                         |                                                                                                                |                                         |        |

| din_byte[                               | 00000000      |                                         |                                         |                                         |                                         |                                         | 00000                                   | 000                                                 |                                         |                                         |                                         |                                                                                                                |                                         |        |

| din_rdy                                 | 0             |                                         |                                         |                                         |                                         |                                         |                                         |                                                     |                                         |                                         |                                         |                                                                                                                |                                         |        |

| { tx_buff[19                            |               |                                         |                                         |                                         |                                         |                                         |                                         | 000000000000000000000000000000000000000             |                                         |                                         |                                         |                                                                                                                |                                         |        |

| test_conr                               |               |                                         |                                         |                                         |                                         |                                         |                                         | 000000000000000000000000000000000000000             |                                         |                                         |                                         |                                                                                                                |                                         |        |

| set_num(                                |               |                                         |                                         |                                         |                                         |                                         |                                         | 323239383830323637                                  |                                         |                                         |                                         |                                                                                                                |                                         |        |

| message[                                |               |                                         |                                         |                                         |                                         |                                         |                                         |                                                     |                                         |                                         |                                         |                                                                                                                |                                         |        |

| in a constant of the                    |               |                                         |                                         |                                         |                                         |                                         |                                         |                                                     |                                         |                                         |                                         |                                                                                                                |                                         |        |

| message_                                | 22439854      |                                         |                                         |                                         |                                         |                                         |                                         |                                                     |                                         |                                         |                                         |                                                                                                                |                                         |        |

| s message_                              | 1=040=00      |                                         |                                         |                                         |                                         | 10000000                                |                                         |                                                     |                                         |                                         |                                         |                                                                                                                |                                         |        |