# CHAPTER 1

# **PROJECT OVERVIEW**

### **PROJECT OVERVIEW**

#### **1.1 INTRODUCTION**

Modern age is the age of computers and all recent equipment are working on the principles of digital communication techniques and efforts have been made to upgrade older equipments to the new standards, hence increasing their service life cycle. This in addition to enhanced efficiency has a pleasant effect on the economy. In this context, one area which has been neglected and holds great potential is military inventory. It includes equipment which may be as big as aeroplanes to radars, tanks and other communication systems. It will save not only foreign exchanges but also a step towards self sufficiency and decrease our dependence on other countries. So we decided to focus our efforts on this department which has been ignored in the past. One such example is AN/TPQ-36 artillery locating radar currently used by artillery.

AN/TPQ-36 is an American radar and a very costly equipment acquired in late 80's. It locates enemy artillery guns and acquires their exact location. Currently it is being operated by an operator who performs all the functions manually i.e. the operator manually plots the coordinates on a map. And then through a radio set passes the information to the concerned parties. This consumes a lot of time and is prone to human errors. The solution to problem is either to acquire the digital map kit from the manufacturer at a handsome cost or to try and develop a much cheaper solution locally. Apart from the cost factor there were other hurdles in the form of the imposed sanctions. C4I has been working on this project and the project undertaken is the endeavour in the same direction.

The first and the most important task is to acquire the data generated by the radar so that it can be used with digital maps. Developing an interface with the radar is a gigantic task. It is so because of the complexity of radar circuitry it self

and non compatibility of its components with modern equipment. Most of the IC's used are unknown and hence in case of malfunction cannot be repaired. Prior to our involvement projects had been undertaken on the same lines which were unsuccessful. Hence there were two options available to us; either to continue with incomplete work of the previous attempts or to develop and implement a design of our own. We decided to go with the second option.

The second important issue is transfer of data generated by the radar after it was transferred to the computer. It requires developing an interface which could link the data with the digital maps. Our problem was some what simplified because we didn't have to digitize the map as we were using the digitized map that is currently being used by the C4I. For this purpose they were using a GIS (Geographical Information System) Geomedia. Our objective was to develop the software that will use the data useful software. The design phase was completed in visual c++ and the code for this is given at the end .

### 1.2 **OVERVIEW**

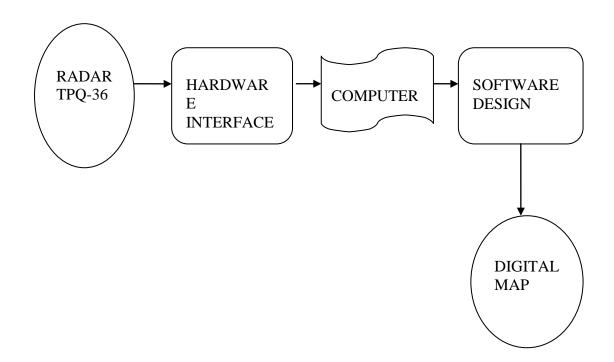

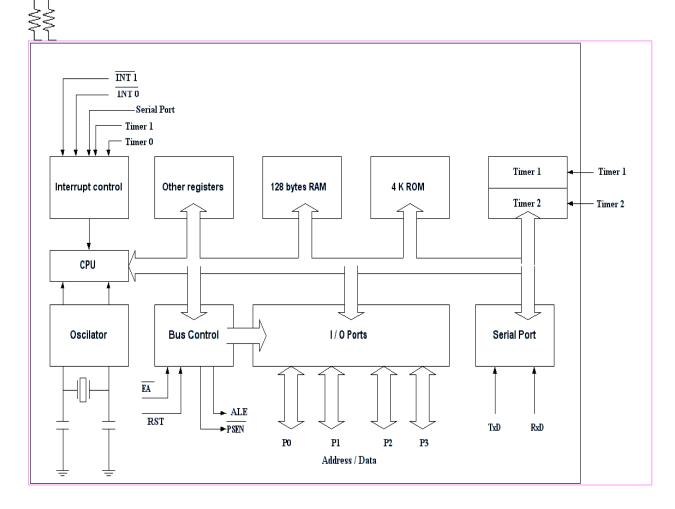

#### FIGURE 1.1 PROJECT OVERVIEW

FIGURE 1.1 shows the modular diagram of the project. The information from the radar (AN/TPQ-36) is fed to the computer through a hardware interface. The main project effort was concentrated in designing and implementing this module. The data was transferred to the computer through its serial port. The emphasis was given to synchronization of the source and the receiver. The parameter which governs the transfer of data is the baud rate. In order to use the data received correctly it had to be converted to a specific format. For this an algorithm in c/visual c++ was written so that it is compatible with the digital map. A software that includes codes for converting data into required format and displaying the location of the gun on the digital map was developed and successfully implemented. The main challenge in the project was its real time implementation. The main issues adhered were synchronization of the transmitter and the receiver.

### **1.3 PROJECT MODULES.**

The project comprised of the following modules.

- Studying the radar

- Selection of data source

- Designing Hardware interface

- Studying computer communication ports

- Study and implementation of Software interface

- C/VC++ coding

- MATLAB based simulation

- Real time implementation

# **CHAPTER 2**

# **STUDY OF RADAR**

## **STUDY OF RADAR**

#### **2.1. INTRODUCTION**

AN/TPQ-36 Firefinder Weapon Locating System general properties.

- Benefits

- Early threat detection from medium standoff ranges

- Detection of multiple threats— mortars, artillery, and rockets

- Support of friendly weapons, reduced fratricide

- Exceptional accuracy

- Superior mobility

- . Rapid emplacement and displacement .

- High system operational availability .

- Reduced maintenance costs and downtime

- Medium-Range Surveillance Raytheon's compact, mobile, combat-proven AN/TPQ-36

- Firefinder radar accurately, rapidly, and automatically locates medium-range • enemy mortars, artillery, and rocket launchers. It can handle simultaneous fire from weapons at multiple locations, detecting and reporting their positions on the first round. No longer must front-line troops and armor be exposed to long periods of enemy mortar, artillery, and rocket attacks. The AN/TPQ-36 directs accurate counterfire to neutralize enemy positions. The AN/TPQ-36's automatic detection, tracking, and locating process is so fast that an enemy weapon's position can often be pinpointed before its projectile impacts. Locations are automatically corrected for Electronic Systems Sometimes the best offense is a good defense. In seconds, the mediumrange AN/TPQ-36 Firefinder Weapon Locating System detects and backplots enemy projectiles and provides pinpoint targeting data for the counterattack. altitude differences, using computer-stored digital maps, and presented to the operator in northing, easting, and altitude coordinates. The system is so automatic and simple to operate that, once set up, the operator need not be present in the operation control shelter to determine a weapon's location. Rounds from friendly weapons also can be tracked, for more accurate delivery. Defeats Enemy Firepower, Supports Friendly Weapons The AN/TPQ-36's stationary antenna sweeps a rapid sequence of beams along the horizon, forming an electronic radar curtain over a 90° area. Any target enetrating the curtain triggers an immediate verification beam. On verification, an automatic tracking sequence begins.AN/TPQ-36 Firefinder Weapon Locating System While tracking any single target, the radar continues scanning, locating, and tracking others. The AN/TPQ-36 can detect and report the positions of up to 10 different weapons in seconds, at a maximum range of 24 km. The system also corrects and improves the delivery of friendly fire. Signal and data processors test each track to filter out birds, aircraft, and other unwanted returns, giving the AN/TPQ-36 an extremely low false-location rate and a very high probability of location. Once the computer establishes a target's validity, it smooths the easured track data, deriving a trajectory that it extrapolates to establish the target's firing

position and impact location. Those data are displayed on a visual map and printed out in map coordinates. From the operation control shelter, the powerdriven antenna can be tilted or rotated to any azimuth position. The system also offers a  $360^{\circ}$  sectoring mode Maximum range: 24 km

#### 2.2 System Capabilities Specifications

Locates mortars, artillery, and rocket launchers Highly Mobile Compact and highly mobile, the AN/TPQ-36 supports rapid deployment of forces and close combat. It can be positioned and ready for operation in 15 minutes. It can be readied for movement in 5 minutes by a five-man crew. Because it can move quickly from one position to another, it is typically located close to the forward battle line in direct support of brigade operations. The AN/TPQ-36 comprises an antenna-transceiver trailer, a generator, and an operation control shelter that contains processing equipment, the weapon-locating unit, and communications equipment. For the U.S. army, the 2,500-lb shelter is carried on a HMMWV or a 2.5-ton truck; however, it can also be carried by other tactical vehicles. The manned operation control shelter can be located as far as Locates 10 weapons simultaneously Locates targets on first round Performs high-burst, datum-plane, and impact registrations Adjusts friendly fire Interfaces with tactical fire Predicts impact of hostile projectiles search one sector for a short period, then automatically rotate in turn to the other sectors.

Effective range

Artillery: 18 km Rockets: 24 km Azimuth sector: 90° Frequency: X-band, 32 frequencies Prime power: 115/200 VAC, 400 Hz, 3-phase, 8 kW Peak transmitted power: 23 kW, minimum 50 m away from the unmanned antenna trailer.

Exceptionally Reliable With high system reliability and maintainability simplified by computercontrolled, built-in test equipment, Raytheon's AN/TPQ-36 provides unusually high system availability. On-line fault detection and off-line fault diagnostics alert the operator to system faults, directing repair action to the unit that must be replaced. Ninety percent of all repairs required in the field can be performed by the crew, with a mean-time-to-repair of only 30 minutes. The AN/TPQ-36's cost effectiveness is enhanced by its 90°–360° sector, small crew, ease of operation, and high availability. The operation control shelter can be used interchangeably with either the AN/TPQ-36 or the longer-range AN/TPQ-37, with only a software change, thereby providing operational flexibility and much greater life-cycle cost effectiveness. Features Permanent storage for 99 targets Field exercise mode Digital data interface.

FIGURE 2 AN/TPQ-36 FIREFINDER

### 2.3 DATA GENERATED BY THE RADAR

AN/TPQ-36 has a computer and supporting PCB which interface the computer with various components such as the line printer , magnetic tape unit,B-scope etc. when operational AN/TPQ-36 locates the exact location of enemy guns and generates the data which is provided to various peripherals through a controller called "Cartridge and Printer controller". Cartridge and Printer controller (CPC) basically controls all the operations regarding the transfer of data to these devices .

### 2.3.1 DATA AT B-SCOPE

The computer sends the data to the B-scope where it is displayed as Easting, northing and altitude. The radar also generates the location of the impact as well.

### 2.3.2 DATA AT WLU(Weapon Location Unit)

The computer sends the same data to the weapon location unit . the format of the data is the same at all three terminals

### 2.3.3 DATA AT LINE PRINTER

computer sends seven bit data and a strobe to the line printer. In return the line printer sends two signals back to the line printer i.e. fault and ready. In simple words handshaking occurs between the printer and the computer through the cartridge and printer controller.

### 2.4 SELECTION OF DATA INPUT DEVICE

Computer sends data to

- B-scope

- WLU

- Line printer

So we had to select a point from which we can extract data with ease . after extensive study we came to the conclusion that line printer was the easiest and safest approach. The reason for the selection of line printer was that B-scope and WLU were difficult to access moreover PCB connected to them were very sensitive and the probability of damaging the components was higher. There was also a possibility of extracting data directly from the computer instead of the peripherals. But this proposal was rejected because an attempt had already been made by AWC(Air Weapon Complex) which was unsuccessful and they damaged some of the PCB's which were expensive. After keeping all these factors in mind we decided to extract data at the input of the line printer.

# CHAPTER 3

# **INTERFACING THROUGH COMPUTER PORTS.**

# a. <u>PARALLEL PORT.</u>

### **3.1 Introduction to Parallel Ports**

The Parallel Port is the most commonly used port for interfacing home made projects. This port will allow the input of up to 9 bits or the output of 12 bits at any one given time, thus requiring minimal external circuitry to implement many simpler tasks. The port is composed of 4 control lines, 5 status lines and 8 data lines. It's found commonly on the back of your PC as a D-Type 25 Pin female connector. There may also be a D-Type 25 pin male connector. This will be a serial RS-232 port and thus, is a totally incompatible port. Newer Parallel Port's are standardized under the IEEE 1284 standard first released in 1994. This standard defines 5 modes of operation which are as follows,

- 1. Compatibility Mode.

- 2. Nibble Mode. (Protocol not Described in this Document)

- 3. Byte Mode. (*Protocol not Described in this Document*)

- 4. EPP Mode (Enhanced Parallel Port).

- 5. ECP Mode (Extended Capabilities Port).

The aim was to design new drivers and devices which were compatible with each other and also backwards compatible with the Standard Parallel Port (SPP). Compatibility, Nibble & Byte modes use just the standard hardware available on the original Parallel Port cards while EPP & ECP modes require additional hardware which can run at faster speeds, while still being downwards compatible with the Standard Parallel Port.

Compatibility mode or "Centronics Mode" as it is commonly known, can only send data in the forward direction at a typical speed of 50 kbytes per second but can be as high as 150+ kbytes a second. In order to receive data, you must change the mode to either

- 1. Nibble or

- 2. Byte mode.

- 1. **Nibble mode** can input a nibble (4 *bits*) in the reverse direction. E.g. from device to computer.

- 2. **Byte mode** uses the Parallel's bi-directional feature (*found only on some cards*) to input a byte (8 *bits*) of data in the reverse direction.

Extended and Enhanced Parallel Ports use additional hardware to generate and manage handshaking. To output a byte to a printer (or anything in that matter) using compatibility mode, the software must.

1. Write the byte to the Data Port.

2. Check to see is the printer is busy. If the printer is busy, it will not accept any data, thus any data which is written will be lost.

3. *Take the Strobe (Pin 1) low. This tells the printer that there is the correct data on the data lines. (Pins 2-9)*

4. Put the strobe high again after waiting approximately 5 microseconds after putting the strobe low. (Step 3)

This limits the speed at which the port can run at. The EPP & ECP ports get around this by letting the hardware check to see if the printer is busy and generate a strobe and /or appropriate handshaking. This means only one I/O instruction need to be performed, thus increasing the speed.

These ports can output at around 1-2 megabytes per second. The ECP port also has the advantage of using DMA channels and FIFO buffers, thus data can be shifted around without using I/O instructions.

### **3.2 Hardware Properties**

The D-Type 25 pin connector is the most common connector found on the Parallel Port of the computer, while the Centronics Connector is commonly found on printers. The IEEE 1284 standard however specifies 3 different connectors for use with the Parallel Port. The first one, 1284 Type A is the D-Type 25 connector found on the back of most computers. The 2nd is the 1284 Type B which is the 36 pin Centronics Connector found on most printers.

| Pin #(D-TYPE | SPP SIGNAL      | DIRECTION | REGISTER | HARDWARE |

|--------------|-----------------|-----------|----------|----------|

| 25)          |                 | IN/OUT    |          | INVERTED |

| 1            | NStrobe         | In/Out    | Control  | Yes      |

| 2            | Data 0          | Out       | Data     |          |

| 3            | Data 1          | Out       | Data     |          |

| 4            | Data 2          | Out       | Data     |          |

| 5            | Data 3          | Out       | Data     |          |

| 6            | Data 4          | Out       | Data     |          |

| 7            | Data 5          | Out       | Data     |          |

| 8            | Data 6          | Out       | Data     |          |

| 9            | Data 7          | Out       | Data     |          |

| 10           | NAck            | In        | Status   |          |

| 11           | Busy            | In        | Status   | Yes      |

| 12           | Paper-out       | In        | Status   |          |

|              | PaperEnd        |           |          |          |

| 13           | Select          | In        | Status   |          |

| 14           | nAuto Linefeed  | In/Out    | Control  | Yes      |

| 15           | nError/nFault   | In        | Status   |          |

| 16           | NInitialize     | In/Out    | Control  |          |

| 17           | nselect-Printer | In/Out    | Control  | Yes      |

|              | nselect-In      |           |          |          |

| 18-25        | Ground          | Gnd       |          |          |

IEEE 1284 Type C however, is a 36 conductor connector like the Centronics, but smaller.

Table 3.1 Pin Assignments of the D-Type 25 pin Parallel Port Connector.

The above table uses "n" in front of the signal name to denote that the signal is active low. e.g. nError. If the printer has occurred an error then this line is low. This line normally is high, should the printer be functioning correctly. The "Hardware Inverted" means the signal is inverted by the Parallel card's hardware. Such an example is the Busy line. If +5v (Logic 1) was applied to this pin and the status register read, it would return back a 0 in Bit 7 of the Status Register.

The output of the Parallel Port is normally TTL logic levels. The voltage levels are the easy part. The current you can sink and source varies from port to port. Most Parallel Ports implemented in ASIC, can sink and source around 12mA. However these are just some of the figures taken from Data sheets, Sink/Source 6mA, Source 12mA/Sink 20mA, Sink 16mA/Source 4mA, Sink/Source 12mA. As you can see they vary quite a bit. The best bet is to use a buffer, so the least current is drawn from the Parallel Port.

### **3.3 Port Addresses**

The Parallel Port has three commonly used base addresses. These are listed in table 2, below. The 3BCh base address was originally introduced used for Parallel Ports on early Video Cards. This address then disappeared for a while, when Parallel Ports were later removed from Video Cards. They has now reappeared as an option for Parallel Ports integrated onto motherboards, upon which their configuration can be changed using BIOS.

LPT1 is normally assigned base address 378h, while LPT2 is assigned 278h. However this may not always be the case as explained later. 378h & 278h have always been commonly used for Parallel Ports. The lower case h denotes that it is in hexadecimal. These addresses may change from machine to machine.

| ADDRESS   | NOTES:                                                                                                                                                                |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3BCh-3BFh | Used for Parallel Ports which were<br>incorporated in to Video Cards and<br>now, commonly an option for Ports<br>controlled by BIOS Doesn't support<br>ECP addresses. |

| 378h-37Fh | Usual Address For LPT 1                                                                                                                                               |

| 278h-27Fh | Usual Address For LPT 2                                                                                                                                               |

Table 3.2 Port Addresses

When the computer is first turned on, BIOS (Basic Input/Output System) will determine the number of ports you have and assign device labels LPT1, LPT2 & LPT3 to them. BIOS first looks at address 3BCh. If a Parallel Port is found here, it is assigned as LPT1, then it searches at location 378h. If a Parallel card is found there, it is assigned the next free device label. This would be LPT1 if a card wasn't found at 3BCh or LPT2 if a card was found at 3BCh. The last *port of call*, is 278h and follows the same procedure than the other two ports. Therefore it is possible to have a LPT2 which is at 378h and not at the expected address 278h.

What can make this even confusing, is that some manufacturers of Parallel Port Cards, have jumpers which allow you to set your Port to LPT1, LPT2, LPT3. Now what address is

LPT1? - On the majority of cards LPT1 is 378h, and LPT2, 278h, but some will use 3BCh as LPT1, 378h as LPT1 and 278h as LPT2. *Life wasn't meant to be easy.*

The assigned devices LPT1, LPT2 & LPT3 should not be a worry to people wishing to interface devices to their PC's. Most of the time the base address is used to interface the port rather than LPT1 etc. However should you want to find the address of LPT1 or any of the Line **P**rinTer Devices, you can use a lookup table provided by BIOS. When BIOS assigns addresses to your printer devices, it stores the address at specific locations in memory, so we can find them.

| FUNCTION                     |

|------------------------------|

| LPT1's Base Address          |

| LPT2's Base Address          |

| LPT3's Base Address          |

| LPT4's Base Address (Note 1) |

|                              |

Table 3.3 - LPT Addresses in the BIOS Data Area

The above table, table 3.3, shows the address at which we can find the Printer Port's addresses in the BIOS Data Area. Each address will take up 2 bytes. The following sample program in C, shows how you can read these locations to obtain the addresses of your printer ports.

```

#include <stdio.h>

#include <dos.h>

void main(void)

unsigned int far *ptraddr; /* Pointer to location of Port Addresses */

unsigned int address; /* Address of Port */

int a;

ptraddr=(unsigned int far *)0x00000408;

for (a = 0; a < 3; a++)

{

address = *ptraddr;

if (address == 0)

printf("No port found for LPT%d \n",a+1);

else

printf("Address assigned to LPT%d is %Xh\n",a+1,address);

*ptraddr++;

}

}

```

Note 1 : Address 0000:040E in the BIOS Data Area may be used as the Extended Bios Data Area in PS/2 and newer Bioses, and thus this field may be invalid.

# 3.4 Software Registers - Standard Parallel Port (SPP)

| OFFSET  | NAME      | <b>READ/WRITE</b> | BIT NO | PROPERTIES    |

|---------|-----------|-------------------|--------|---------------|

| BASE +0 | DATA PORT | WRITE (Note 1)    | Bit 7  | Data 7(Pin 9) |

|         |           |                   | Bit 6  | Data 6(Pin 8) |

|         |           |                   | Bit 5  | Data 5(Pin 7) |

|         |           |                   | Bit 4  | Data 4(Pin 6) |

|         |           |                   | Bit 3  | Data 3(Pin 5) |

|         |           |                   | Bit 2  | Data 2(Pin 4) |

|         |           |                   | Bit 1  | Data 1(Pin 3) |

|         |           |                   | Bit 0  | Data 0(Pin 2) |

Table 3.4 Data Port

Note 1 : If the Port is bi-directional then Read and Write Operations can be performed on the Data Register.

The base address, usually called the Data Port or Data Register is simply used for outputting data on the Parallel Port's data lines (Pins 2-9). This register is normally a write only port. If you read from the port, you should get the last byte sent. However if your port is bi-directional, you can receive data on this address. See *Bi-directional Ports* for more detail.

| BASE +1 | STATUS PORT | READ ONLY | Bit 7 | Busy      |

|---------|-------------|-----------|-------|-----------|

|         |             |           | Bit 6 | Ack       |

|         |             |           | Bit 5 | Paper out |

|         |             |           | Bit 4 | Select in |

|         |             |           | Bit 3 | Error     |

|         |             |           | Bit 2 | IRQ       |

|         |             |           | Bit 1 | Reserved  |

|         |             |           | Bit 0 | Reserved  |

Table 3.5 Status Port

The Status Port (base address + 1) is a read only port. Any data written to this port will be ignored. The Status Port is made up of 5 input lines (Pins 10,11,12,13 & 15), a IRQ status register and two reserved bits. Please note that Bit 7 (Busy) is a active low input. E.g. If bit 7 happens to show a logic 0, this means that there is +5v at pin 11. Likewise with Bit 2. (nIRQ) If this bit shows a '1' then an interrupt has **not** occurred.

| BASE +2 | CONTROL PORT | READ\WRITE | Bit 7 | Unused                     |

|---------|--------------|------------|-------|----------------------------|

|         |              |            | Bit 6 | Unused                     |

|         |              |            | Bit 5 | Enable bi-directional port |

|         |              |            | Bit 4 | Enable IRQ via Ack line    |

|         |              |            | Bit 3 | Select printer             |

|         |              |            | Bit 2 | Initialize printer (Reset) |

|         |              |            | Bit 1 | Auto linefeed              |

|         |              |            | Bit 0 | Strobe                     |

Table 3.6 Control Port

The Control Port (base address + 2) was intended as a write only port. When a printer is attached to the Parallel Port, four "controls" are used. These are Strobe, Auto Linefeed, Initialize and Select Printer, all of which are inverted except Initialize.

The printer would not send a signal to initialize the computer, nor would it tell the computer to use auto linefeed. However these four outputs can also be used for inputs. If the computer has placed a pin high (e.g. +5v) and your device wanted to take it low, you would effectively short out the port, causing a conflict on that pin. Therefore these lines are "open collector" outputs (*or open drain for CMOS devices*). This means that it has two states. A low state (0v) and a high impedance state (open circuit).

Normally the Printer Card will have internal pull-up resistors, but as you would expect, not all will. Some may just have open collector outputs, while others may even have normal totem pole outputs. In order to make your device work correctly on as many Printer Ports as possible, you can use an external resistor as well. Should you already have an internal resistor, then it will act in Parallel with it, or if you have Totem pole outputs, the resistor will act as a load.

An external 4.7k resistor can be used to pull the pin high. I wouldn't use anything lower, just in case you do have an internal pull up resistor, as the external resistor would act in parallel giving effectively, a lower value pull up resistor. When in high impedance state the pin on the Parallel Port is high (+5v). When in this state, your external device can pull the pin low and have the control port change read a different value. This way the 4 pins of the Control Port can be used for bi-directional data transfer. However the Control Port must be set to xxxx0100 to be able to read data, that is all pins to be +5v at the port so that you can pull it down to GND (logic 0).

Bits 4 & 5 are internal controls. Bit four will enable the IRQ (*See Using the Parallel Ports IRQ*) and Bit 5 will enable the bi-directional port meaning that you can input 8 bits using (DATA0-7). This mode is only possible if your card supports it. Bits 6 & 7 are reserved. Any writes to these two bits will be ignored.

# b. SERIAL PORT

### 3.5 Introduction

The Serial Port is harder to interface than the Parallel Port. In most cases, any device you connect to the serial port will need the serial transmission converted back to parallel so that it can be used. This can be done using a UART. On the software side of things, there are many more registers that you have to attend to than on a Standard Parallel Port. (SPP) So what are the advantages of using serial data transfer rather than parallel?

- 1. Serial Cables can be longer than Parallel cables. The serial port transmits a '1' as -3 to -25 volts and a '0' as +3 to +25 volts where as a parallel port transmits a '0' as 0v and a '1' as 5v. Therefore the serial port can have a maximum swing of 50V compared to the parallel port which has a maximum swing of 5 Volts. Therefore cable loss is not going to be as much of a problem for serial cables than they are for parallel.

- 2. You don't need as many wires than parallel transmission. If your device needs to be mounted a far distance away from the computer then 3 core cable (Null Modem Configuration) is going to be a lot cheaper that running 19 or 25 core cable. However you must take into account the cost of the interfacing at each end.

- 3. Infra Red devices have proven quite popular recently. You may of seen many electronic diaries and palmtop computers which have infra red capabilities build in. However could you imagine transmitting 8 bits of data at the one time across the room and being able to (from the devices point of view) decipher which bits are which? Therefore serial transmission is used where one bit is sent at a time. IrDA-1 (The first infra red specifications) was capable of 115.2k baud and was interfaced into a UART. The pulse length however was cut down to 3/16th of a RS232 bit length to conserve power considering these devices are mainly used on diaries, laptops and palmtops.

- 4. Microcontroller's have also proven to be quite popular recently. Many of these have in built SCI (Serial Communications Interfaces) which can be used to talk to the outside world. Serial Communication reduces the pin count of these MPU's. Only two pins are commonly used, Transmit Data (TXD) and Receive Data (RXD) compared with at least 8 pins if you use a 8 bit Parallel method (You may also require a Strobe).

### **3.6 Hardware Properties**

Devices which use serial cables for their communication are split into two categories. These are DCE (Data Communications Equipment) and DTE (Data Terminal Equipment.) Data Communications Equipment are devices such as your modem, TA adapter, plotter etc while Data Terminal Equipment is your Computer or Terminal.

The electrical specifications of the serial port is contained in the EIA (Electronics Industry Association) RS232C standard. It states many parameters such as -

- 1. A "Space" (logic 0) will be between +3 and +25 Volts.

- 2. A "Mark" (Logic 1) will be between -3 and -25 Volts.

- 3. The region between +3 and -3 volts is undefined.

- 4. An open circuit voltage should never exceed 25 volts. (In Reference to GND)

- 5. A short circuit current should not exceed 500mA. The driver should be able to handle this without damage. (Take note of this one!)

Above is no where near a complete list of the EIA standard. Line Capacitance, Maximum Baud Rates etc are also included. For more information please consult the EIA RS232-E standard. It is interesting to note however, that the RS232C standard specifies a maximum baud rate of 20,000 BPS!, which is rather slow by today's standards. Revised standards, EIA-232D & EIA-232E were released, in 1987 & 1991 respectively.

Serial Ports come in two "sizes", There are the D-Type 25 pin connector and the D-Type 9 pin connector both of which are male on the back of the PC, thus you will require a female connector on your device. Below is a table of pin connections for the 9 pin and 25 pin D-Type connectors.

| D-Type 25 Pin No | D-Type 9Pin No | Abbreviations | Full Name           |

|------------------|----------------|---------------|---------------------|

| Pin 2            | Pin 3          | TD            | Transmit Data       |

| Pin 3            | Pin 2          | RD            | Receive Data        |

| Pin 4            | Pin 7          | RTS           | Request to send     |

| Pin 5            | Pin 8          | CTS           | Clear to send       |

| Pin 6            | Pin 6          | DSR           | Data send ready     |

| Pin 7            | Pin 5          | SG            | Signal ground       |

| Pin 8            | Pin 1          | CD            | Carrier detect      |

| Pin 20           | Pin 4          | DTR           | Data terminal ready |

| Pin 22           | Pin 9          | RI            | Ring indicator      |

## **3.6.1** Serial Pinouts (D25 and D9 Connectors)

Table 3.8 : D Type 9 Pin and D Type 25 Pin Connectors

## **3.6.2** Pin Functions

| Abbreviations | Full Name           | Functions                                 |

|---------------|---------------------|-------------------------------------------|

| TD            | Transmit Data       | Serial data output (TXD)                  |

| RD            | Receive Data        | Serial data input (RXD)                   |

| DCD           | Data carrier detect | When the data detects Carrier from the    |

|               |                     | modem at the other end of the phone line, |

|               |                     | this Line becomes active.                 |

| CTS           | Clear to send       | This line indicate that modem is ready to |

|               |                     | exchange data.                            |

| DSR           | Data send ready     | This tells the UART that the modem is     |

|               |                     | ready to establish the link.              |

| DTR | Data terminal ready | This is opposite to DSR. This tells the |

|-----|---------------------|-----------------------------------------|

|     |                     | modem that the UART is ready to link.   |

| RTS | Request to send     | This line informs the modem that the    |

|     |                     | UART is ready to exchange data.         |

| RI  | Ring indicator      | Goes active when the modem detects the  |

|     |                     | ringing signal from the PSTN.           |

### 3.7 Null Modems

A Null Modem is used to connect two DTE's together. This is commonly used as a cheap way to network games or to transfer files between computers using Zmodem Protocol, Xmodem Protocol etc. This can also be used with many Microprocessor Development Systems.

| D25 |                             |                                                      | D25                                                  | D9                                                   |

|-----|-----------------------------|------------------------------------------------------|------------------------------------------------------|------------------------------------------------------|

| 2   | TD                          | $\longrightarrow$ RD                                 | 3                                                    | 2                                                    |

| 3   | $RD \leftarrow \cdots$      | TD                                                   | 2                                                    | 3                                                    |

| 7   | SG ←                        | $\longrightarrow$ SG                                 | 7                                                    | 5                                                    |

| 20  | DTR —                       | - DTR                                                | 20                                                   | 4                                                    |

| 6   | $DSR \leftarrow$            | $\rightarrow DSR$                                    | б                                                    | б                                                    |

| 8   | CD 🚽                        | $ ightarrow c_D$                                     | 8                                                    | 1                                                    |

| 4   | RTS —                       | _ RTS                                                | 4                                                    | 7                                                    |

| 5   | CTS ←                       | ightarrow cts                                        | 5                                                    | 8                                                    |

|     | 2<br>3<br>7<br>20<br>6<br>8 | $\begin{array}{cccccccccccccccccccccccccccccccccccc$ | $\begin{array}{cccccccccccccccccccccccccccccccccccc$ | $\begin{array}{cccccccccccccccccccccccccccccccccccc$ |

Figure 3.4 : Null Modem Wiring Diagram

Above is my preferred method of wiring a Null Modem. It only requires 3 wires (TD, RD & SG) to be wired straight through thus is more cost effective to use with long cable runs. The theory of operation is reasonably easy. The aim is to make to computer think it is talking to a modem rather than another computer. Any data transmitted from the first computer must be received by the second thus TD is connected to RD. The second computer must have the same set-up thus RD is connected to TD. Signal Ground (SG) must also be connected so both grounds are common to each computer.

The Data Terminal Ready is looped back to Data Set Ready and Carrier Detect on both computers. When the Data Terminal Ready is asserted active, then the Data Set Ready and Carrier Detect immediately become active. At this point the computer thinks the Virtual Modem to which it is connected is ready and has detected the carrier of the other modem.

All left to worry about now is the Request to Send and Clear To Send. As both computers communicate together at the same speed, flow control is not needed thus these two lines are also linked together on each computer. When the computer wishes to send data, it asserts the Request to Send high and as it's hooked together with the Clear to Send, It immediately gets a reply that it is ok to send and does so.

Notice that the ring indicator is not connected to anything of each end. This line is only used to tell the computer that there is a ringing signal on the phone line. As we don't have a modem connected to the phone line this is left disconnected.

## 3.8 LoopBack Plug

This loopback plug can come in extremely handy when writing Serial / RS232 Communications Programs. It has the receive and transmit lines connected together, so that anything transmitted out of the Serial Port is immediately received by the same port. If you connect this to a Serial Port an load a Terminal Program, anything you type will be immediately displayed on the screen. This can be used with the examples later in this tutorial.

| D9     | D25      | TD               |

|--------|----------|------------------|

| 3      | 2        | TD —             |

| 2<br>5 | 3        | RD 🚽             |

| 5      | 7        | SG               |

| 4      | 20       | DTR —            |

| б      | 6        | $DSR \leftarrow$ |

| 1      | 8        | CD 🚽             |

| 7      | 4        | RTS —            |

| 8      | 5        | CTS ←            |

|        | Figure 3 | 3.5              |

LoopBack Plug

### **3.9 DTE / DCE Speeds**

We have already talked briefly about DTE & DCE. A typical Data Terminal Device is a computer and a typical Data Communications Device is a Modem. Often people will talk about DTE to DCE or DCE to DCE speeds. DTE to DCE is the speed between your modem and computer, sometimes referred to as your terminal speed. This should run at faster speeds than the DCE to DCE speed. DCE to DCE is the link between modems, sometimes called the line speed.

Most people today will have 28.8K or 33.6K modems. Therefore we should expect the DCE to DCE speed to be either 28.8K or 33.6K. Considering the high speed of the modem we should expect the DTE to DCE speed to be about 115,200 BPS. (Maximum Speed of the 16550a UART) This is where some people often fall into a trap. The communications program which they use have settings for DCE to DTE speeds. However they see 9.6 KBPS, 14.4 KBPS etc and think it is your modem speed.

Today's Modems should have Data Compression build into them. This is very much like PK-ZIP but the software in your modem compresses and decompresses the data. When set up correctly you can expect compression ratios of 1:4 or even higher. 1 to 4 compression would be typical of a text file. If we were transferring that text file at 28.8K (DCE-DCE), then when the modem compresses it you are actually transferring 115.2 KBPS between computers and thus have a DCE-DTE speed of 115.2 KBPS.

Thus this is why the DCE-DTE should be much higher than your modem's connection speed. Some modem manufacturers quote a maximum compression ratio as 1:8. Lets say for example its on a new 33.6 KBPS modem then we may get a maximum 268,800 BPS transfer between modem and UART. If you only have a 16550a which can do 115,200 BPS tops, then

you would be missing out on a extra bit of performance. Buying a 16C650 should fix your problem with a maximum transfer rate of 230,400 BPS.

However don't abuse your modem if you don't get these rates. These are MAXIMUM compression ratios. In some instances if you try to send a already compressed file, your modem can spend more time trying the compress it, thus you get a transmission speed less than your modem's connection speed. If this occurs try turning off your data compression. This should be fixed on newer modems. Some files compress easier than others thus any file which compresses easier is naturally going to have a higher compression ratio.

### 3.10 Flow Control

So if our DTE to DCE speed is several times faster than our DCE to DCE speed the PC can send data to your modem at 115,200 BPS. Sooner or later data is going to get lost as buffers overflow, thus flow control is used. Flow control has two basic varieties, Hardware or Software.

Software flow control, sometimes expressed as Xon/Xoff uses two characters Xon and Xoff. Xon is normally indicated by the ASCII 17 character where as the ASCII 19 character is used for Xoff. The modem will only have a small buffer so when the computer fills it up the modem sends a Xoff character to tell the computer to stop sending data. Once the modem has room for more data it then sends a Xon character and the computer sends more data. This type of flow control has the advantage that it doesn't

require any more wires as the characters are sent via the TD/RD lines. However on slow links each character requires 10 bits which can slow communications down.

Hardware flow control is also known as RTS/CTS flow control. It uses two wires in your serial cable rather than extra characters transmitted in your data lines. Thus hardware flow control will not slow down transmission times like Xon-Xoff does. When the computer wishes to send data it takes active the Request to Send line. If the modem has room for this data, then the modem will reply by taking active the Clear to Send line and the computer starts sending data. If the modem does not have the room then it will not send a Clear to Send.

# c. <u>PARALLEL TO SERIAL DATA CONVERSION</u>

### **3.11** The UART (8250 and Compatibles)

UART stands for Universal Asynchronous Receiver / Transmitter. Its the little box of tricks found on your serial card which plays the little games with your modem or other connected devices. Most cards will have the UART's integrated into other chips which may also control your parallel port, games port, floppy or hard disk drives and are typically surface mount devices. The 8250 series, which includes the 16450, 16550, 16650, & 16750 UARTS are the most commonly found type in your PC. Later we will look at other types which can be used in your homemade devices and projects.

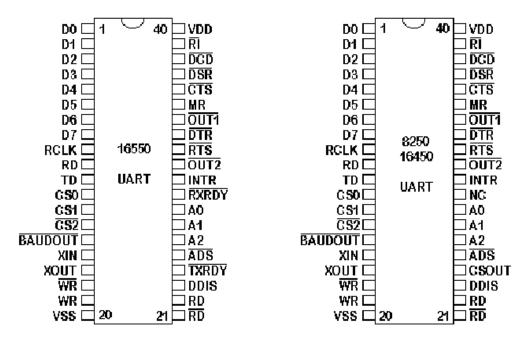

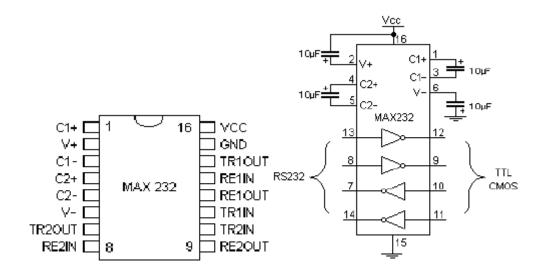

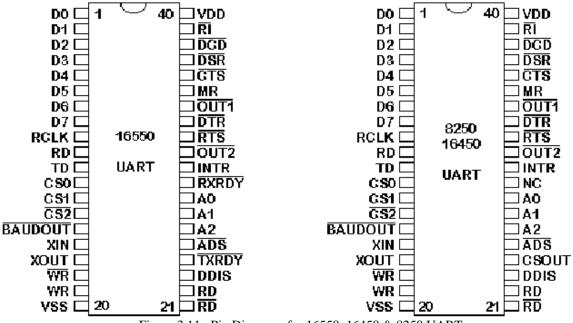

Figure 3.6 : Pin Diagrams for 16550, 16450 & 8250 UARTs

The 16550 is chip compatible with the 8250 & 16450. The only two differences are pins 24 & 29. On the 8250 Pin 24 was chip select out which functioned only as a indicator to if the chip was active or not. Pin 29 was not connected on the 8250/16450 UARTs. The 16550 introduced two new pins in their place. These are Transmit Ready and Receive Ready which can be implemented with DMA (Direct Memory Access). These Pins have two different modes of operation. Mode 0 supports single transfer DMA where as Mode 1 supports Multi-transfer DMA.

Mode 0 is also called the 16450 mode. This mode is selected when the FIFO buffers are disabled via Bit 0 of the FIFO Control Register or When the FIFO buffers are enabled but DMA Mode Select = 0. (Bit 3 of FCR) In this mode RXRDY is active low when at least one character (Byte) is present in the Receiver Buffer. RXRDY will go inactive high when no more characters are left in the Receiver Buffer. TXRDY will be active low when there are no characters in the

Transmit Buffer. It will go inactive highafter the first character / byte is loaded into the Transmit Buffer.

Mode 1 is when the FIFO buffers are active and the DMA Mode Select = 1. In Mode 1, RXRDY will go active low when the trigger level is reached or when 16550 Time Out occurs and will return to inactive state when no more characters are left in the FIFO. TXRDY will be active when no characters are present in the Transmit Buffer and will go inactive when the FIFO Transmit Buffer is completely Full.

All the UARTs pins are TTL compatible. That includes TD, RD, RI, DCD, DSR, CTS, DTR and RTS which all interface into your serial plug, typically a D-type connector. Therefore RS232 Level Converters (which we talk about in detail later) are used. These are commonly the DS1489 Receiver and the DS1488 as the PC has +12 and -12 volt rails which can be used by these devices. The RS232 Converters will convert the TTL signal into RS232 Logic Levels.

The UART requires a Clock to run. If you look at your serial card a common crystal found is either a 1.8432 MHZ or a 18.432 MHZ Crystal. The crystal in connected to the XIN-XOUT pins of the UART using a few extra components which help the crystal to start oscillating. This clock will be used for the Programmable Baud Rate Generator which directly interfaces into the transmit timing circuits but not directly into the receiver timing circuits. For this an external connection mast be made from pin 15 (BaudOut) to pin 9 (Receiver clock in.) Note that the clock signal will be at Baudrate 16.

| Pin No. | Name     | Notes                                                                                                                                         |

|---------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| Pin 1:8 | D0:D7    | Data Bus                                                                                                                                      |

| Pin 9   | RCLK     | Receiver Clock Input. The frequency of this input should equal the receivers baud rate * 16                                                   |

| Pin 10  | RD       | Receive Data                                                                                                                                  |

| Pin 11  | TD       | Transmit Data                                                                                                                                 |

| Pin 12  | CS0      | Chip Select 0 - Active High                                                                                                                   |

| Pin 13  | CS1      | Chip Select 1 - Active High                                                                                                                   |

| Pin 14  | nCS2     | Chip Select 2 - Active Low                                                                                                                    |

| Pin 15  | nBAUDOUT | Baud Output - Output from Programmable Baud Rate Generator.<br>Frequency = (Baud Rate x 16)                                                   |

| Pin 16  | XIN      | External Crystal Input - Used for Baud Rate Generator Oscillator                                                                              |

| Pin 17  | XOUT     | External Crystal Output                                                                                                                       |

| Pin 18  | nWR      | Write Line - Inverted                                                                                                                         |

| Pin 19  | WR       | Write Line - Not Inverted                                                                                                                     |

| Pin 20  | VSS      | Connected to Common Ground                                                                                                                    |

| Pin 21  | RD       | Read Line - Inverted                                                                                                                          |

| Pin 22  | nRD      | Read Line - Not Inverted                                                                                                                      |

| Pin 23  | DDIS     | Driver Disable. This pin goes low when CPU is reading from UART.<br>Can be connected to Bus Transceiver in case of high capacity data<br>bus. |

| Pin 24  | nTXRDY   | Transmit Ready                                                                                                                                |

| Pin 25  | nADS     | Address Strobe. Used if signals are not stable during read or write cycle                                                                     |

| Pin 26  | A2       | Address Bit 2                                                                                                                                 |

| Pin 27  | A1       | Address Bit 1                                                                                                                                 |

| Pin 28  | A0       | Address Bit 0                                                                                                                                 |

| Pin 29 | nRXRDY | Receive Ready       |  |

|--------|--------|---------------------|--|

| Pin 30 | INTR   | Interrupt Output    |  |

| Pin 31 | nOUT2  | User Output 2       |  |

| Pin 32 | nRTS   | Request to Send     |  |

| Pin 33 | nDTR   | Data Terminal Ready |  |

| Pin 34 | nOUT1  | User Output 1       |  |

| Pin 35 | MR     | Master Reset        |  |

| Pin 36 | nCTS   | Clear To Send       |  |

| Pin 37 | nDSR   | Data Set Ready      |  |

| Pin 38 | nDCD   | Data Carrier Detect |  |

| Pin 39 | nRI    | Ring Indicator      |  |

| Pin 40 | VDD    | + 5 Volts           |  |

Table 3.9 : Pin Assignments for 16550A UART

# **3.11.1** Types of UARTS (For PC's)

| 8250           | First UART in this series. It contains no scratch register. The 8250A was an improved version of the 8250 which operates faster on the bus side. |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| 8250A          | This UART is faster than the 8250 on the bus side. Looks exactly the same                                                                        |

| 9 <b>25</b> 0D | to software than 16450.                                                                                                                          |

| 8250B          | Very similar to that of the 8250 UART.                                                                                                           |

| 16450          | Used in AT's (Improved bus speed over 8250's). Operates comfortably at                                                                           |

|                | 38.4KBPS. Still quite common today.                                                                                                              |

| 16550          | This was the first generation of buffered UART. It has a 16 byte buffer,                                                                         |

|                | however it doesn't work and is replaced with the 16550A.                                                                                         |

| 16550A         | Is the most common UART use for high speed communications eg 14.4K                                                                               |

|                | & 28.8K Modems. They made sure the FIFO buffers worked on this                                                                                   |

|                | UART.                                                                                                                                            |

| 16650          | Very recent breed of UART. Contains a 32 byte FIFO, Programmable X-                                                                              |

|                | On / XOff characters and supports power management.                                                                                              |

| 16750          | Produced by Texas Instruments. Contains a 64 byte FIFO.                                                                                          |

| NAME  | ADDRESS | IRQ |

|-------|---------|-----|

| COM 1 | 3F8     | 4   |

| COM 2 | 2F8     | 3   |

| COM 3 | 3E8     | 4   |

| COM 4 | 2E8     | 3   |

### 3.11.2 Serial Port's Registers (PC's) Port Addresses & IRQ's

Table 3.10 : Standard Port Addresses

Above is the standard port addresses. These should work for most P.C's. If you just happen to be lucky enough to own a IBM P/S2 which has a micro-channel bus, then expect a different set of addresses and IRQ's. Just like the LPT ports, the base addresses for the COM ports can be read from the BIOS Data Area.

| START ADDRESS | FUNCTION             |

|---------------|----------------------|

| 0000 : 0400   | COM 1's Base Address |

| 0000 : 0402   | COM 2's Base Address |

| 0000 : 0404   | COM 3's Base Address |

| 0000 : 0406   | COM 4's Base Address |

Table 3.11 - COM Port Addresses in the BIOS Data Area;

The above table shows the address at which we can find the Communications (COM) ports addresses in the BIOS Data Area. Each address will take up 2 bytes. The following sample program in C, shows how you can read these locations to obtain the addresses of your communications ports.

```

#include <stdio.h>

#include <dos.h>

void main(void)

unsigned int far *ptraddr; /* Pointer to location of Port Addresses */

unsigned int address; /* Address of Port */

int a;

ptraddr=(unsigned int far *)0x00000400;

for (a = 0; a < 4; a++)

{

address = *ptraddr;

if (address == 0)

printf("No port found for COM%d \n",a+1);

else

printf("Address assigned to COM%d is %Xh\n",a+1,address);

*ptraddr++;

}

```

| Base Address | DLAB | Read/Write | Abr. | Register Name                     |

|--------------|------|------------|------|-----------------------------------|

| + 0          | =0   | Write      | -    | Transmitter Holding Buffer        |

|              | =0   | Read       | -    | Receiver Buffer                   |

|              | =1   | Read/Write | -    | Divisor Latch Low Byte            |

| + 1          | =0   | Read/Write | IER  | Interrupt Enable Register         |

|              | =1   | Read/Write | -    | Divisor Latch High Byte           |

| + 2          | -    | Read       | IIR  | Interrupt Identification Register |

|              | -    | Write      | FCR  | FIFO Control Register             |

| + 3          | -    | Read/Write | LCR  | Line Control Register             |

| + 4          | -    | Read/Write | MCR  | Modem Control Register            |

| + 5          | -    | Read       | LSR  | Line Status Register              |

| + 6          | -    | Read       | MSR  | Modem Status Register             |

| + 7          | -    | Read/Write | -    | Scratch Register                  |

**3.11.3 Table of Registers**

Table 3.12 : Table of Registers

## 3.11.4 DLAB?

You will have noticed in the table of registers that there is a DLAB column. When DLAB is set to '0' or '1' some of the registers change. This is how the UART is able to have 12 registers (including the scratch register) through only 8 port addresses. DLAB stands for Divisor Latch Access Bit. When DLAB is set to '1' via the line control register, two registers become available from which you can set your speed of communications measured in bits per second.

The UART will have a crystal which should oscillate around 1.8432 MHZ. The UART incorporates a divide by 16 counter which simply divides the incoming clock signal by 16. Assuming we had the 1.8432 MHZ clock signal, that would leave us with a maximum, 115,200 hertz signal making the UART capable of transmitting and receiving at 115,200 Bits Per Second (BPS). That would be fine for some of the faster modems and devices which can handle that speed, but others just wouldn't communicate at all. Therefore the UART is fitted with a Programmable Baud Rate Generator which is

controlled by two registers.

Lets say for example we only wanted to communicate at 2400 BPS. We worked out that we would have to divide 115,200 by 48 to get a workable 2400 Hertz Clock. The "Divisor", in this case 48, is stored in the two registers controlled by the "Divisor Latch Access Bit". This divisor

can be any number which can be stored in 16 bits (ie 0 to 65535). The UART only has a 8 bit data bus, thus this is where the two registers are used. The first register (Base + 0) when DLAB = 1 stores the "Divisor latch low byte" where as the second register (base + 1 when DLAB = 1) stores the "Divisor latch high byte."

| Speed (BPS) | Divisor (Dec) | Divisor Latch High Byte | Divisor Latch Low Byte |

|-------------|---------------|-------------------------|------------------------|

| 50          | 2304          | 09h                     | 00h                    |

| 300         | 384           | 01h                     | 80h                    |

| 600         | 192           | 00h                     | C0h                    |

| 2400        | 48            | 00h                     | 30h                    |

| 4800        | 24            | 00h                     | 18h                    |

| 9600        | 12            | 00h                     | 0Ch                    |

| 19200       | 6             | 00h                     | 06h                    |

| 38400       | 3             | 00h                     | 03h                    |

| 57600       | 2             | 00h                     | 02h                    |

| 115200      | 1             | 00h                     | 01h                    |

Below is a table of some more common speeds and their divisor latch high bytes & low bytes. Note that all the divisors are shown in Hexadecimal.

Table 3.13 : Table of Commonly Used Baudrate Divisors

# 3.11.5 Interrupt Enable Register (IER)

| Notes                                            |                                                                                                                                                                                                                                               |  |  |

|--------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Reserved                                         |                                                                                                                                                                                                                                               |  |  |

| Reserved                                         |                                                                                                                                                                                                                                               |  |  |

| Enable low power mode (16750)                    |                                                                                                                                                                                                                                               |  |  |

| Enables sleep mode(16750)                        |                                                                                                                                                                                                                                               |  |  |

| Enable modem status interrupt                    |                                                                                                                                                                                                                                               |  |  |

| Enable receive line status interrupt             |                                                                                                                                                                                                                                               |  |  |

| Enable transmit holding register empty interrupt |                                                                                                                                                                                                                                               |  |  |

| Enable received data available interrupt         |                                                                                                                                                                                                                                               |  |  |

| -                                                | Reserved         Reserved         Enable low power mode (16750)         Enables sleep mode(16750)         Enable modem status interrupt         Enable receive line status interrupt         Enable transmit holding register empty interrupt |  |  |

Table 3.14 : Interrupt Enable Register

The Interrupt Enable Register could possibly be one of the easiest registers on a UART to understand. Setting Bit 0 high enables the Received Data Available Interrupt which generates an interrupt when the receiving register/FIFO contains data to be read by the CPU.

Bit 1 enables Transmit Holding Register Empty Interrupt. This interrupts the CPU when the transmitter buffer is empty. Bit 2 enables the receiver line status interrupt. The UART will interrupt when the receiver line status changes. Likewise for bit 3 which enables the modem status interrupt. Bits 4 to 7 are the easy ones. They are simply reserved. (If only everything was that easy!)

| Bit        |           | Notes                                          |                          |  |  |

|------------|-----------|------------------------------------------------|--------------------------|--|--|

| Bits 6 : 7 | Bit 6     | Bit 7                                          |                          |  |  |

|            | 0         | 0 No FIFO                                      |                          |  |  |

|            | 0         | 1 FIFO Enabled but Unusable                    |                          |  |  |

|            | 1         | 1 FIFO Enabled                                 |                          |  |  |

| Bit 5      | 64 Byte I | ifo Enabled (16750 only)                       |                          |  |  |

| Bit 4      | Reserved  |                                                |                          |  |  |

| Bit 3      | 0         | Reserved                                       | on 8250, 16450           |  |  |

|            | 1         | 16550 Ti                                       | me-out Interrupt Pending |  |  |

| Bits 1 : 2 | Bit 2     | Bit 1                                          |                          |  |  |

|            | 0         | 0 Modem Status Interrupt                       |                          |  |  |

|            | 0         | 1 Transmitter Holding Register Empty Interrupt |                          |  |  |

|            | 1         | 0 Received Data Available Interrupt            |                          |  |  |

|            | 1         | 1 Receiver Line Status Interrupt               |                          |  |  |

| Bit 0      | 0         | Interrupt Pending                              |                          |  |  |

|            | 1         | No Interr                                      | upt Pending              |  |  |

## 3.11.6 Interrupt Identification Register (IIR)

Table 3.15 : Interrupt Identification Register

The interrupt identification register is a read only register. Bits 6 and 7 give status on the FIFO Buffer. When both bits are '0' no FIFO buffers are active. This should be the only result you will get from a 8250 or 16450. If bit 7 is active but bit 6 is not active then the UART has it's buffers enabled but are unusable. This occurs on the 16550 UART where a bug in the FIFO buffer made the FIFO's unusable. If both bits are '1' then the FIFO buffers are enabled and fully operational.

Bits 4 and 5 are reserved. Bit 3 shows the status of the time-out interrupt on a 16550 or higher. Lets jump to Bit 0 which shows whether an interrupt has occurred. If an interrupt has occurred it's status will shown by bits 1 and 2. These interrupts work on a priority status. The Line Status Interrupt has the highest Priority, followed by the Data Available Interrupt, then the

Transmit Register Empty Interrupt and then the Modem Status Interrupt which has the lowest priority.

| Bit        | Notes                                                                       |       |                         |  |  |

|------------|-----------------------------------------------------------------------------|-------|-------------------------|--|--|

| Bits 6 : 7 | Bit 7                                                                       | Bit 6 | Interrupt Trigger Level |  |  |

|            | 0                                                                           | 0     | 1 Byte                  |  |  |

|            | 0 1 4 Bytes                                                                 |       |                         |  |  |

|            | 1 0 8 Bytes                                                                 |       |                         |  |  |

|            | 1                                                                           | 1     | 14 Bytes                |  |  |

| Bit 5      | Enable 64 Byte FIFO (16750 only)                                            |       |                         |  |  |

| Bit 4      | Reserved                                                                    |       |                         |  |  |

| Bit 3      | DMA Mode Select. Change status of RXRDY & TXRDY pins from mode 1 to mode 2. |       |                         |  |  |

| Bit 2      | Clear Transmit FIFO                                                         |       |                         |  |  |

| Bit 1      | Clear Receive FIFO                                                          |       |                         |  |  |

| Bit 0      | Enable FII                                                                  | FO's  |                         |  |  |

| 3.11.7 First In / First Out Control Register (FCR) |

|----------------------------------------------------|

|----------------------------------------------------|

Table 3.16 : FIFO Control Register

The FIFO register is a write only register. This register is used to control the FIFO (First In / First Out) buffers which are found on 16550's and higher.

Bit 0 enables the operation of the receive and transmit FIFO's. Writing a '0' to this bit will disable the operation of transmit and receive FIFO's, thus you will loose all data stored in these FIFO buffers.

Bit's 1 and 2 control the clearing of the transmit or receive FIFO's. Bit 1 is responsible for the receive buffer while bit 2 is responsible for the transmit buffer. Setting these bits to 1 will only clear the contents of the FIFO and will not affect the shift registers. These two bits are self resetting, thus you don't need to set the bits to '0' when finished.

Bit 3 enables the DMA mode select which is found on 16550 UARTs and higher. More on this later. Bits 4 and 5 are those easy type again, Reserved.

Bits 6 and 7 are used to set the triggering level on the Receive FIFO. For example if bit 7 was set to '1' and bit 6 was set to '0' then the trigger level is set to 8 bytes. When there is 8 bytes of data in the receive FIFO then the Received Data Available interrupt is set. See (IIR)

## 3.11.8 Line Control Register (LCR)

The Line Control register sets the basic parameters for communication. Bit 7 is the Divisor Latch Access Bit or DLAB for short. We have already talked about what it does. (See DLAB?) Bit 6 Sets break enable. When active, the TD line goes into "Spacing" state which causes a break in the receiving UART.Setting this bit to '0' Disables the Break.Bits 3,4 and 5 select parity. If you study the 3 bits, you will find that bit 3 controls parity. That is, if it is set to '0' then no parity is used, but if it is set to '1' then parity is used. Jumping to bit 5, we can see that it controls sticky parity. Sticky parity is simply when the parity bit is always transmitted and checked as a '1' or '0'. This has very little success in checking for errors as if the first 4 bits contain errors but the sticky parity bit contains the appropriately set bit, then a parity error will not result. Sticky high parity is the use of a '1' for the parity bit, while the opposite, sticky low parity is the use of a '0' for the parity bit. If bit 5 controls sticky parity, then turning this bit off must produce normal parity provided bit 3 is still set to '1'. Odd parity is when the parity bit is transmitted as a '1' or '0' so that there is a odd number of 1's. Even parity must then be the parity bit produces and even number of 1's. This provides better error checking but still is not perfect, thus CRC-32 is often used for software error correction. If one bit happens to be inverted with even or odd parity set, then a parity error will occur, however if two bits are flipped in such a way that it produces the correct parity bit then an parity error will no occur.

Bit 2 sets the length of the stop bits. Setting this bit to '0' will produce one stop bit, however setting it to '1' will produce either 1.5 or 2 stop bits depending upon the word length. Note that the receiver only checks the first stop bit.Bits 0 and 1 set the word length. This should be pretty straight forward. A word length of 8 bits is most commonly used today.

| Bit        |        | Notes                                                                        |   |                     |  |

|------------|--------|------------------------------------------------------------------------------|---|---------------------|--|

| Bit 7      | 1      | Divisor Latch Access Bit                                                     |   |                     |  |

|            | 0      | Access to Receiver buffer, Transmitter buffer & Interrupt<br>Enable Register |   |                     |  |

| Bit 6      | Set Br | eak Enable                                                                   |   |                     |  |

| Bits 3 : 5 | Bit 5  | Bit 4 Bit 3 Parity Select                                                    |   | Parity Select       |  |

|            | Х      | Х                                                                            | 0 | No Parity           |  |

|            | 0      | 0 1                                                                          |   | Odd Parity          |  |

|            | 0      | 1 1 1                                                                        |   | Even Parity         |  |

|            | 1      | 0 1 High Parity (Sticky)                                                     |   |                     |  |

|            | 1      | 1                                                                            | 1 | Low Parity (Sticky) |  |

| Bit 2      | Length of Stop Bit |                                                                                               |        |  |  |  |

|------------|--------------------|-----------------------------------------------------------------------------------------------|--------|--|--|--|

|            | 0                  | One Stop Bit                                                                                  |        |  |  |  |

|            | 1                  | 2 Stop bits for words of length 6,7 or 8 bits or 1.5 Stop<br>Bits for Word lengths of 5 bits. |        |  |  |  |

| Bits 0 : 1 | Bit 1              | Bit 0 Word Length                                                                             |        |  |  |  |

|            | 0                  | 0                                                                                             | 5 Bits |  |  |  |

|            | 0                  | 1 6 Bits                                                                                      |        |  |  |  |

|            | 1                  | 0 7 Bits                                                                                      |        |  |  |  |

|            | 1                  | 1                                                                                             | 8 Bits |  |  |  |

Table 3.17 : Line Control Register

| Bit   | Notes                                 |

|-------|---------------------------------------|

| Bit 7 | Reserved                              |

| Bit 6 | Reserved                              |

| Bit 5 | Autoflow Control Enabled (16750 only) |

| Bit 4 | LoopBack Mode                         |

| Bit 3 | Aux Output 2                          |

| Bit 2 | Aux Output 1                          |

| Bit 1 | Force Request to Send                 |

| Bit 0 | Force Data Terminal Ready             |

**3.11.9** Modem Control Register (MCR)

Table 3.18 : Modem Control Register

The Modem Control Register is a Read/Write Register. Bits 5,6 and 7 are reserved. Bit 4 activates the loopback mode. In Loopback mode the transmitter serial output is placed into marking state. The receiver serial input is disconnected. The transmitter out is looped back to the receiver in. DSR, CTS, RI & DCD are disconnected. DTR, RTS, OUT1 & OUT2 are connected to the modem control inputs. The modem control output pins are then place in an inactive state. In this mode any data which is placed in the transmitter registers for output is received by the receiver circuitry on the same chip and is available at the receiver buffer. This can be used to test the UARTs operation.

Aux Output 2 maybe connected to external circuitry which controls the UART-CPU interrupt process. Aux Output 1 is normally disconnected, but on some cards is used to switch between a 1.8432MHZ crystal to a 4MHZ crystal which is used for MIDI. Bits 0 and 1 simply control their relevant data lines. For example setting bit 1 to '1' makes the request to send line active.

### 3.11.10 Line Status Register (LSR)

The line status register is a read only register. Bit 7 is the error in received FIFO bit. This bit is high when at least one break, parity or framing error has occurred on a byte which is contained in the FIFO.When bit 6 is set, both the transmitter holding register and the shift register are empty. The UART's holding register holds the next byte of data to be sent in parallel fashion. The shift register is used to convert the byte to serial, so that it can be transmitted over one line. When bit 5 is set, only the transmitter holding register is empty. So what's the difference between the two? When bit 6, the transmitter holding and shift registers are empty, no serial conversions are taking place so there should be no activity on the transmit data line. When

bit 5 is set, the transmitter holding register is empty, thus another byte can be sent to the data port, but a serial conversion using the shift register may be taking place.

| Bit   | Notes                              |

|-------|------------------------------------|

| Bit 7 | Error in Received FIFO             |

| Bit 6 | Empty Data Holding Registers       |

| Bit 5 | Empty Transmitter Holding Register |

| Bit 4 | Break Interrupt                    |

| Bit 3 | Framing Error                      |

| Bit 2 | Parity Error                       |

| Bit 1 | Overrun Error                      |

| Bit 0 | Data Ready                         |

Table 3.19 : Line Status Register